# Over 3 GW/cm<sup>2</sup> Low Leakage Vertical $\beta$ -Ga<sub>2</sub>O<sub>3</sub> Schottky Rectifier Featuring Self-Aligned Multi-Zone Junction Termination Extension

Jiangbin Wan<sup>1</sup>, Hengyu Wang<sup>1\*</sup>, Tiancheng Tao<sup>1</sup>,

Haoyuan Cheng<sup>1</sup>, Ce Wang<sup>1</sup>, Chi Zhang<sup>1</sup> & Kuang Sheng<sup>1, 2\*</sup>

<sup>1</sup>College of Electrical Engineering, Zhejiang University, Hangzhou, 310027, China

<sup>2</sup>ZJU-Hangzhou Global Scientific and Technological Innovation Center, Zhejiang University, China

## Appendix A Design and simulation

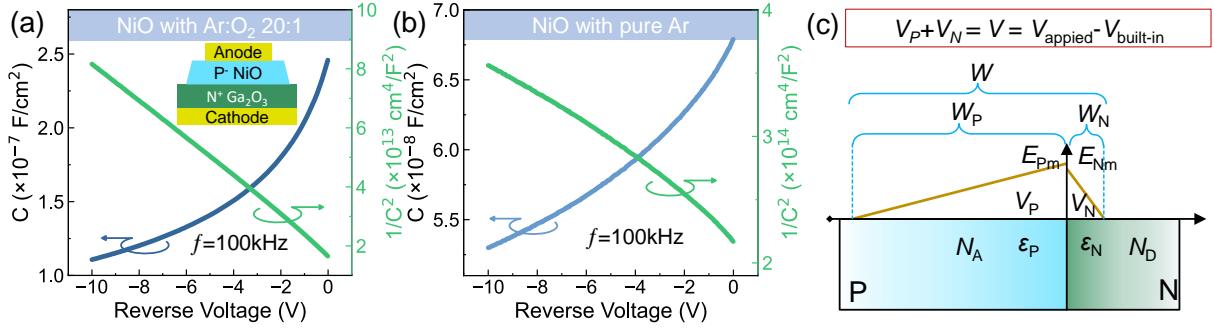

### Appendix A.1 NiO parameter extraction

In this subsection, we would like to talk about the NiO parameter extraction through the C-V curves. The two types NiO's C-V on a N<sup>+</sup> Ga<sub>2</sub>O<sub>3</sub> substrate are also presented in Figure A1(a) and (b). These curves can allow us to extract the NiO parameter in actual application scenarios. Here, we are going to introduce the detailed derivation process and talk about the equations for hetero-junctions as follows. In Figure A1(c), we have presented the schematic view of the hetero-junction with an applied voltage of  $V_{\text{applied}}$ . Before derivation, let's first introduce the definition of each variable.

- $N_A$ : the doping of the P-type semiconductor,

- $N_D$ : the doping of the N-type semiconductor,

- $E_{Pm}$ : the peak electric field at the P-type side of the hetero-interface,

- $E_{Nm}$ : the peak electric field at the N-type side of the hetero-interface,

- $\epsilon_P$ : the dielectric constant of the P-type semiconductor,

- $\epsilon_N$ : the dielectric constant of the N-type semiconductor,

- $V$ : the actual voltage applied on the hetero-junction ( $V=V_{\text{applied}}-V_{\text{built-in}}$ ),

- $V_{\text{applied}}$ : external applied voltage by external testing equipment,

- $V_{\text{built-in}}$ : the built-in potential of the hetero-junction, which can be obtained through the C-V,

- $V_P$ : the voltage on the P-type semiconductor,

- $V_N$ : the voltage on the N-type semiconductor,

- $W$ : the depletion width of the heterojunction,

- $W_P$ : the depletion width of the heterojunction at the P-type side,

- $W_N$ : the depletion width of the heterojunction at the N-type side,

- $D$ : the electric displacement vector across the hetero-interface,

According to the Poisson's equation, the peak E-field at the heterojunction interface can be calculated:

$$E_{Pm} = \frac{qN_A W_P}{\epsilon_P} = \sqrt{\frac{2qN_A V_P}{\epsilon_P}} \quad (A1)$$

$$E_{Nm} = \frac{qN_D W_N}{\epsilon_N} = \sqrt{\frac{2qN_D V_N}{\epsilon_N}} \quad (A2)$$

So, the applied voltage on the P and N semiconductor can be calculated:

$$V_P = \frac{qN_A W_P^2}{2\epsilon_P} \quad (A3)$$

$$V_N = \frac{qN_D W_N^2}{2\epsilon_N} \quad (A4)$$

And for the E-field pass the heterojunction interface, the electric displacement vector ( $D$ ) is the same:

$$D = \epsilon_N E_{Nm} = \epsilon_P E_{Pm} \quad (A5)$$

\* Corresponding author (email: wanghengyu@zju.edu.cn, shengk@zju.edu.cn)

**Figure A1** CV characteristic of the NiO on a N<sup>+</sup> Ga<sub>2</sub>O<sub>3</sub> substrate for the parameter extraction. (a) NiO with Ar:O<sub>2</sub> ratio of 20:1, (b) NiO with pure Ar. (c) The schematic view of the hetero-junction under reverse bias.

Then, the applied voltage on the total hetero-junction can be calculated as:

$$V = V_P + V_N = \frac{D}{2} \left( \frac{W_P}{\varepsilon_P} + \frac{W_N}{\varepsilon_N} \right) \quad (\text{A6})$$

According to above equations, it can be conducted that the depletion width for P and N are:

$$W_P = \sqrt{\frac{2\varepsilon_P\varepsilon_N N_D V}{qN_A(\varepsilon_P N_A + \varepsilon_N N_D)}} \quad (\text{A7})$$

$$W_N = \sqrt{\frac{2\varepsilon_P\varepsilon_N N_A V}{qN_D(\varepsilon_P N_A + \varepsilon_N N_D)}} \quad (\text{A8})$$

After that, we can directly get the depletion width:

$$W = W_P + W_N = \sqrt{\frac{2\varepsilon_P\varepsilon_N (N_A + N_D)^2 V}{qN_A N_D (\varepsilon_P N_A + \varepsilon_N N_D)}} \quad (\text{A9})$$

Importantly, we can calculate the C according to:

$$C = \frac{\varepsilon_P}{W_P} + \frac{\varepsilon_N}{W_N} \quad (\text{A10})$$

Then we can get the NiO average doping concentration through the C-V curves by solving the equation with unknown variables as NiO doping. The donor doping of the highly-doped Ga<sub>2</sub>O<sub>3</sub> substrate presented in Figure 2 is about  $1 \times 10^{19} \text{ cm}^{-3}$ . After that, the average P-type doping of the NiO with Ar:O<sub>2</sub> (20:1) and pure Ar are calculated and determined to be  $\sim 1.8 \times 10^{18} \text{ cm}^{-3}$  and  $\sim 3 \times 10^{17} \text{ cm}^{-3}$ , respectively.

### Appendix A.2 JTE design principle

In this section, we are going to talk about the JTE design principle. We assume that the length of JTE is long enough to ensure that the electric field in the JTE's transition region between the termination and active region approximately satisfies the electric field of a one-dimensional parallel-plane junction. In the ideal parallel-plane junction, the charges in the N-type side and P-type side are balanced and complementary, which means their charges are equal in any blocking state. This means the total P-type dose is equal to the N-type dose. So we are going to get the following equations according to the Poisson's equation:

$$qN_{\text{P, total}} t_{\text{P, total}} = q(N_{\text{layer1}} t_{\text{layer1}} + N_{\text{layer2}} t_{\text{layer2}} + N_{\text{layer3}} t_{\text{layer3}}) = E_N \varepsilon_N \quad (\text{A11})$$

where the  $q$  is the unit charge;  $N_{\text{P, total}}$  and  $t_{\text{P, total}}$  are the equivalent total charge dose;  $N_{\text{layer1}}$ ,  $N_{\text{layer2}}$ , and  $N_{\text{layer3}}$  are the P-type doping concentration in layer 1, layer 2, and layer 3, respectively (each in  $\text{cm}^{-3}$ );  $t_{\text{layer1}}$ ,  $t_{\text{layer2}}$ , and  $t_{\text{layer3}}$  are the corresponding thickness for each layer;  $E_N$  is junction electric field in the N-type semiconductor;  $\varepsilon_N$  is the dielectric constant of the N-type semiconductor.

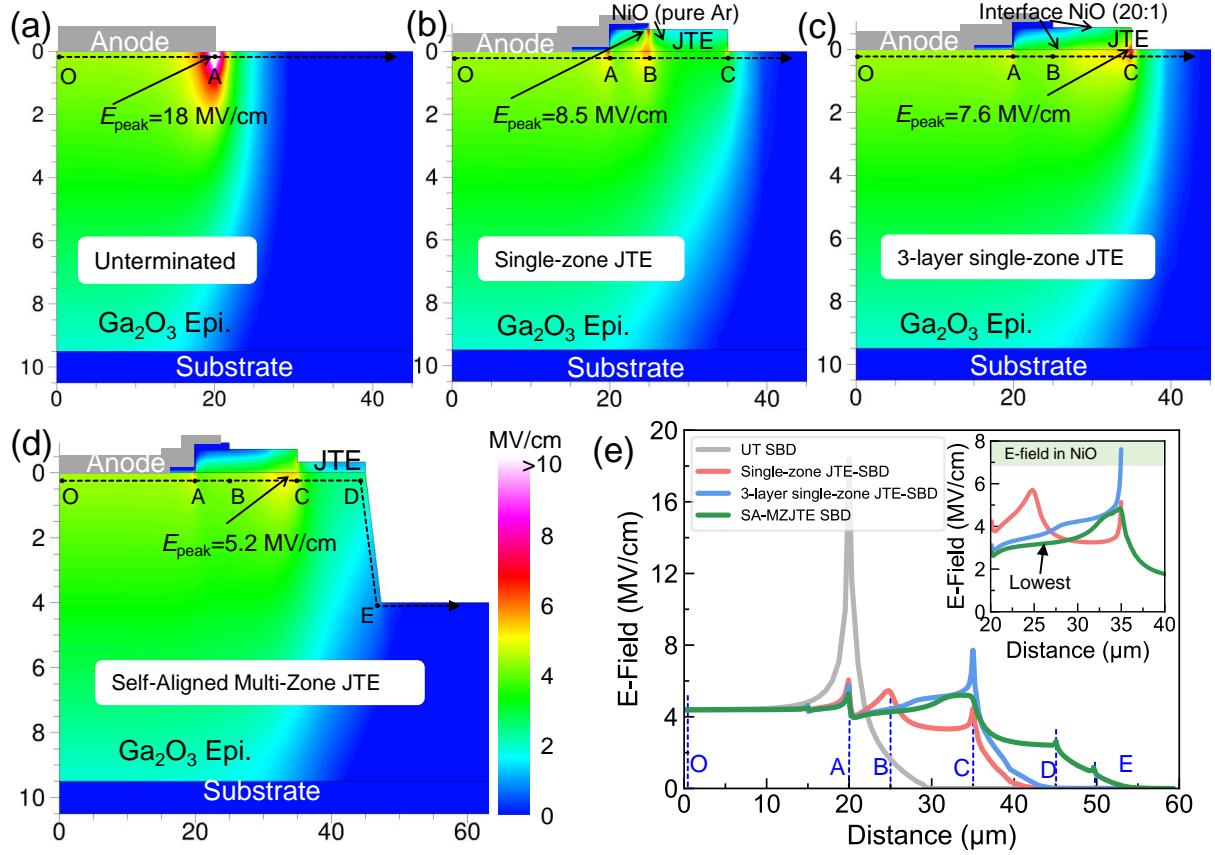

### Appendix A.3 Device simulations

After illustrating the parameter extraction and JTE design principle, we can design the JTE dose. According to previous studied [1], the peak electric field of the NiO/Ga<sub>2</sub>O<sub>3</sub> at the JTE is lower than 4 MV/cm. Here, due to the improved SA-MZJTE design, we assume the peak electric field to be 5 MV/cm. And according to the Eq. (A11) and derived NiO doping, we can determine the NiO thickness to be 20 nm, 600 nm, and 80 nm for layer1, layer2, and layer3 in the simulations for the 3-layer JTE design.

Technology Computer Aided Design (TCAD) simulations were performed using Sentaurus to investigate the proposed SA-MZJTE under a reverse bias of 3000 V. The drift doping Ga<sub>2</sub>O<sub>3</sub> and NiO doping are the same as the experimental value

**Figure A2** Simulated electric field distributions of the (a) UT-SBD, (b) single-zone JTE-SBD, 3-layer single-zone JTE-SBD, and (d) SA-MZJTE SBD with the  $L_{JTE}$  of 10  $\mu\text{m}$ . (d) Extracted E-field profile of the UT-SBD, single-zone JTE-SBD, 3-layer single-zone JTE-SBD, and SA-MZJTE SBD in  $\text{Ga}_2\text{O}_3$  along the cutline O-A-B-C-D-E, which can be seen in Figure 2(a)-(d). The above simulations are conducted at 3000 V reverse bias. Inset: the electric field in NiO at a distance of 50nm away from the hetero-junction interface.

shown in Figure 1(b) and Figure A1, respectively. Figure A2 (a)-(d) depict the electric field distribution of the unterminated SBD (UT-SBD), single-zone JTE-SBD, 3-layer single-zone JTE-SBD, and the proposed SA-MZJTE SBD. The UT-SBD is just a SBD without termination. The single-zone JTE-SBD is the device with 700 nm pure Ar NiO served as a single-zone JTE. The 3-layer single-zone JTE-SBD has a JTE architecture with 20nm 20:1 NiO (layer1), 600 nm pure Ar NiO(layer2), and 80 nm 20:1 NiO(layer3), respectively. The layout of the 3-layer can be found in Figure 1(a) in the manuscript. The SA-MZJTE SBD have the same JTE architecture with 3-layer single-zone JTE-SBD, but it has a multi-zone extension through self-aligned technology. The results indicate that the proposed termination technique effectively reduces the electric field in  $\text{Ga}_2\text{O}_3$ . Meanwhile, compared with single-zone JTE without 20:1 NiO at the hetero-interface, it can effectively reduce the electric field in NiO from 8.5 MV/cm to 5 MV/cm, thus having better blocking capability.

For the 3-layer single-zone JTE-SBD, the JTE dose can't be fully compensated at 3 kV, resulting in the electric field crowding at the JTE edge. The electric field profiles along the cutline O-A-B-C-D-E are presented in Figure A2(e). It is noteworthy that while there is minimal difference in the electric field between JTE and SA-MZJTE in  $\text{Ga}_2\text{O}_3$ , the electric field in NiO for the SA-MZJTE is lower, which is expected to enhance device performance. The extracted electric field in NiO at a distance of 50 nm away from the hetero-junction interface is also presented at the inset figure of Figure A2(e). It can be seen that with the proposed SA-MZJTE, the electric field in NiO can be effectively reduced. These findings demonstrate the effectiveness of the proposed and fabricated SA-MZJTE SBD.

## Appendix B Experiment

The process started with surface treatment to enhance interface quality. Then, a Ti/Au (50/200 nm) metal stack was deposited, followed by a rapid thermal annealing at 500  $^{\circ}\text{C}$  to form an ohmic contact. Subsequently, a 3-layer NiO is deposited to serve as JTE. The deposition details for the three layers are as follows: 20 nm with an Ar: $\text{O}_2$  ratio of 20:1, 600 nm with pure Ar, 80nm with an Ar: $\text{O}_2$  ratio of 20:1. To achieve accurate control of the NiO layer, the NiO deposition rate for the pure Ar NiO and 20:1 NiO are 2 nm/min and 1 nm/min, respectively. The first layer of 20 nm NiO is intended to enhance breakdown field at the surface, improving compatibility with  $\text{Ga}_2\text{O}_3$ . The second layer of 600 nm NiO allows for precise control of the JTE dose, while the third layer of 80 nm NiO is designed to prevent complete depletion of the JTE. Following the deposition of 3-layer JTE, a 10 minutes post-sputter annealing was performed at 300  $^{\circ}\text{C}$  in  $\text{N}_2$  to improve

the hetero-interface quality. An additional 100 nm NiO was then deposited in an Ar/O<sub>2</sub> (2:1) atmosphere with a deposition rate of 0.9 nm/min. Next, a Ni/Au (100/200nm) metal stack was deposited to form Schottky contact. Photoresist was subsequently applied as a protective mask to selectively etch the 3-layer single-zone JTE. At the edge of NiO JTE, the NiO layer inherently acted as a self-aligned mask for etching Ga<sub>2</sub>O<sub>3</sub>, further alleviating electric field crowding at the JTE edges. After removing the residual photoresist with acetone, the SA-MZJTE SBD is successfully fabricated.

## Appendix C Results and discussions

Table 1 benchmarks key metrics of >2 kV Ga<sub>2</sub>O<sub>3</sub> SBD. The device shows  $5 \times 10^{-6}$  A/cm<sup>2</sup> at a reverse bias of 2000 V, which is also among the lowest in >2 kV Ga<sub>2</sub>O<sub>3</sub> SBDs.

**Table C1** Structure and metrics comparison of >2 kV Ga<sub>2</sub>O<sub>3</sub> vertical power SBDs

| Reference | Termination          | $R_{ON,sp}$<br>(mΩ·cm <sup>2</sup> ) | BV<br>(kV) | PFOM <sup>1)</sup><br>(GW/cm <sup>2</sup> ) | Leakage current<br>@2000 V (A/cm <sup>2</sup> ) | Leakage current<br>@2500 V (A/cm <sup>2</sup> ) |

|-----------|----------------------|--------------------------------------|------------|---------------------------------------------|-------------------------------------------------|-------------------------------------------------|

| [2]       | Field plate          | 8.8                                  | 2.89       | 0.95                                        | 6E-5                                            | 1E-3                                            |

| [3]       | High-k + Field plate | 8                                    | 2.34       | 0.68                                        | 5E-4                                            | Breakdown                                       |

| [4]       | Mesa                 | 7.33                                 | 2.73       | 1.01                                        | 2E-5                                            | 6E-4                                            |

| [5]       | Mesa + Field plate   | 3.78                                 | 2.5        | 1.65                                        | 1E-2                                            | 1.0                                             |

| [6]       | JTE                  | 5.9                                  | 2.55       | 1.1                                         | 1E-2                                            | 0.7                                             |

| [7]       | JTE                  | 2.9                                  | 2.11       | 1.52                                        | 2E-2                                            | Breakdown                                       |

| [8]       | Mesa + Field plate   | 3.4                                  | 6          | 10.5                                        | 1E-6                                            | 3E-6                                            |

| This work | JTE                  | 3.2                                  | 3.11       | 3.02                                        | 5E-6                                            | 9E-5                                            |

Based on the wafer parameters and the measured BV, the device parallel-plate junction E-field is calculated. The one-dimensional parallel-plate junction E-field ( $E_J$ ) can be calculated based on the punch-through E-field profile:

$$BV = E_J t_{Ga2O3} - qN_D \times \frac{t_{Ga2O3}^2}{2\epsilon_N} \quad (C1)$$

where  $BV$  is the measured breakdown voltage,  $E_J$  is the one-dimensional parallel-plate junction E-field,  $t_{Ga2O3}$  is the thickness of the Ga<sub>2</sub>O<sub>3</sub> drift layer,  $N_D$  is the net doping of the drift layer,  $\epsilon_N$  is the dielectric constant [6]. According to the Eq. (12), the  $E_J$  of the SA-MZJTE SBD is about 4.53 MV/cm.

## References

- 1 Ma Y W, Qin Y, Porter M, et al. Wide-Bandgap Nickel Oxide with Tunable Acceptor Concentration for Multidimensional Power Devices. *Adv. Electron. Mater.* 2025, 11: 2300662

- 2 Li W, Nomoto K, Hu Z, et al. Field-plated Ga<sub>2</sub>O<sub>3</sub> trench Schottky barrier diodes with a BV2/Ron,sp of up to 0.95 GW/cm<sup>2</sup>. *IEEE Electron Device Lett.* 2020, 41: 107-110

- 3 Farzana E, Roy S, Hendricks N, et al. Vertical PtOx /Pt/β-Ga<sub>2</sub>O<sub>3</sub> Schottky diodes with high permittivity dielectric field plate for low leakage and high breakdown voltage. *Appl. Phys. Lett.* 2023, 123: 192102

- 4 Han Z, Jian G, Zhou X, et al. 2.7 kV Low Leakage Vertical PtOx/β-Ga<sub>2</sub>O<sub>3</sub> Schottky Barrier Diodes With Self-Aligned Mesa Termination. *IEEE Electron Device Letters.* 2023, 44: 1680-1683

- 5 Wan J, Wang H, Wang C, et al. 2.5kV/3.78mΩ·cm<sup>2</sup> Low Forward Voltage Vertical β-Ga<sub>2</sub>O<sub>3</sub> Schottky Rectifier With Field Plate Assisted Deep Mesa Termination. *IEEE Electron Device Lett.* 2024, 45: 778-781

- 6 Wang B, Xiao M, Spencer J, et al. 2.5 kV Vertical Ga<sub>2</sub>O<sub>3</sub> Schottky Rectifier With Graded Junction Termination Extension. *IEEE Electron Device Letters.* 2023, 44: 221-224

- 7 Hao W, Wu F, Li W, et al. Improved Vertical β-Ga<sub>2</sub>O<sub>3</sub> Schottky Barrier Diodes With Conductivity-Modulated p-NiO Junction Termination Extension. *IEEE Transactions on Electron Devices.* 2023, 70: 2129-2134

- 8 Dong P, Zhang J, Yan Q, et al. 6 kV/3.4 mΩ·cm<sup>2</sup> Vertical β-Ga<sub>2</sub>O<sub>3</sub> Schottky Barrier Diode With BV2/Ron,sp Performance Exceeding 1-D Unipolar Limit of GaN and SiC. *IEEE Electron Device Letters.* 2022, 43: 765-768

1) Power Figure of Merit (PFOM) =  $BV^2/R_{ON,sp}$