• Supplementary File •

## $32 \times 32 \beta$ -Ga<sub>2</sub>O<sub>3</sub> MOS solar-blind ultraviolet detector array and its properties

Haifeng Chen<sup>1\*</sup>, Chenlu Wu<sup>1</sup>, Xuyang Liu<sup>1</sup>, Chunling Chen<sup>1</sup>, Huorong Wang<sup>2</sup>, Qin Lu<sup>1</sup>, Xiangtai Liu<sup>1</sup>, Jinyu Ni<sup>3</sup>, Zhan Wang<sup>1</sup> & Shaoqing Wang<sup>1</sup>

<sup>1</sup>Key Laboratory of Advanced Semiconductor Devices and Materials, School of Electronic Engineering, Xi'an University of Posts and Telecommunications, Xi'an 710121, China;

<sup>2</sup>Xi'an Nova StarTech Co, Ltd, Xi'an 710061, China;

<sup>3</sup>China Nanhu Academy of Electronics and Information Technology, Jiaxing 314000, China

## Appendix A MOS Array Fabrication

Si-doped  $Ga_2O_3$  film and  $Al_2O_3$  layer were prepared by ALD. The metal sources were triethylgallium (TEG) and trimethylaluminum (TMA). Tris-dimethylamino silane (TDMASi) was the Si source and the O sources was all ozone (O<sub>3</sub>). While the substrate temperature during deposition was fixed at 250°C. The base pressure of the vacuum chamber was kept below 0.5 Torr and the carrier gas was Ar (20 sccm). The applied ALD cycles of  $Al_2O_3$  layer were 500 while the ALD cycles of  $Ga_2O_3$  film were maintained at 2000 (20 out of the 2000 cycles were Si-doping cycles). The specific array preparation process is as follows. Si-doped  $Ga_2O_3$  film with 100 nm thickness was deposited first on the  $SiO_2$  substrate by ALD and changed into  $\beta$ - $Ga_2O_3$  by annealing at 900 °C for 10 min under nitrogen atmosphere. Then, the film was etched into isolated regions through wet etching with 60 wt%  $H_3PO_4$ . Subsequently, the first photolithography and evaporation of metal (Ti/Au (100/50 nm)) were performed, which was used to prepare the source/drain (S/D) electrodes as well as the row wires in the array. Then this Ti/Au metal layer was rapidly annealed to improve its Ohmic contact performance. Afterwards, an  $Al_2O_3$  gate oxide layer with 50 nm thickness was grown by ALD and etched with 8 wt% HF. Finally, the second photolithography and evaporation of metal (Ni (150 nm)) were applied to prepare the gate electrodes (G) and column wires.

The single pixel unit size is 170  $\mu$ m  $\times$  200  $\mu$ m. The MOSFET has 100-nm-thick Ga<sub>2</sub>O<sub>3</sub> channel layer and 50-nm-thick Al<sub>2</sub>O<sub>3</sub> gate oxide. The length and width of channel are 30  $\mu$ m and 90  $\mu$ m, respectively. At the cross point of S/D and G electrodes in the array, 50-nm-thick Al<sub>2</sub>O<sub>3</sub> layer acts as the electrical isolation layer.

## Appendix B Basic photoelectric characteristic

The characteristics of the MOSFET array were measured by Keysight B1505A semiconductor analyzer. A UV mercury lamp with a wavelength of 254 nm was used for photo response measurements. In the text, the parameter  $\tau_r$  is defined as the time for the photocurrent to increase from 10% to 90% of its maximum value, and decay time  $\tau_d$  is defined as the time for the photocurrent to decrease from 90% to 10% of its maximum value.  $\tau_u$  and  $\tau_f$  are defined similarly.

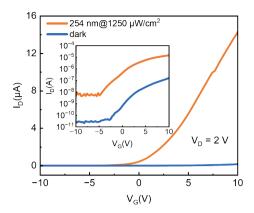

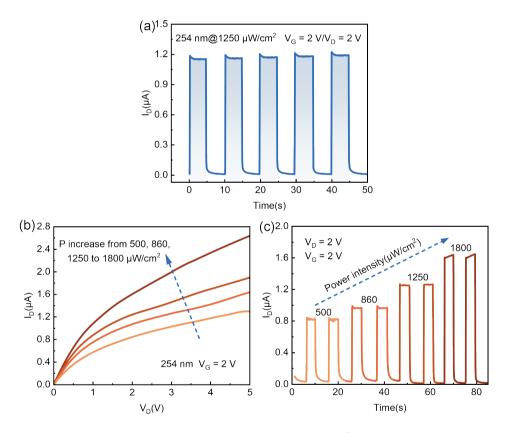

Fig.B1 shows  $I_D$ - $V_G$  curve at  $V_D=2$  V. The semi-logarithmic curves are shown in the inset of Fig.B1, which exhibits a gate modulation of approximately  $10^4$  of device in the dark case. Fig.B2(a) shows the current-time (I-T) curves of the device when both  $V_G$  and  $V_D=2$  V under P of  $1250~\mu W/cm^2$ , which shows that the device has good reproducibility in photo response. Fig.B2(b) shows the variation of the device output curves as P increases from 500 to  $1800~\mu W/cm^2$  at  $V_G=2$  V.  $I_D$  increases with P because a larger P generates more photo-generated carriers. Fig.B2(c) shows the I-T curves in the case of  $V_G=2$  V/ $V_D=2$  V under different P. The growth trend of  $I_D$  with increasing P is consistent with Fig.B2(b). Note that the device exhibits stable transient response characteristics. As P increases from 500 to  $1800~\mu W/cm^2$ ,  $I_D$  are 0.84, 1.07, 1.24 and  $1.60~\mu A$ , respectively.

## Appendix C The gate voltage regulation

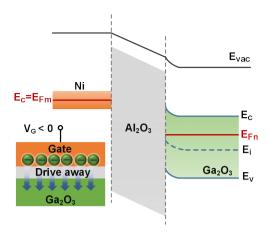

Fig.C1 shows the energy band diagram of the gate oxide layer and  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> film when V<sub>G</sub> < 0. When a negative VG is applied, the energy band of the Ga<sub>2</sub>O<sub>3</sub> film bends upward near the contact interface with the Al<sub>2</sub>O<sub>3</sub> layer. Since the majority carriers of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> as an N-type substrate are electrons, the negative gate voltage repels electrons. This results in a decrease in the surface electron concentration and the device being in an off state, which contributes to the suppression of the I<sub>D</sub>. By extension, this technique can be used to act as electronic shutter. To be more specific, gate can actively turn off the optical response function of the device during continuously UV light irradiation. The faster the gate-controlled response speed, the more multiple images can be collected within a unit of time.

$<sup>\</sup>hbox{$^*$ Corresponding author (email: chenhaifeng@xupt.edu.cn)}\\$

Figure B1  $I_D$ -V $_G$  curves measured under dark and 254 nm UV conditions. The inset shows the  $I_D$ -V $_G$  curves in semi-logarithmic coordinate.

Figure B2 (a)  $I_D$ -T curves when  $V_G=2$   $V/V_D=2$  V under P of 1250  $\mu$ W/cm<sup>2</sup>. (b)  $I_D$ - $V_D$  curves under different P when  $V_G=2$  V. (c)  $I_D$ -T curves under different P when  $V_D=2$   $V/V_G=2$  V.

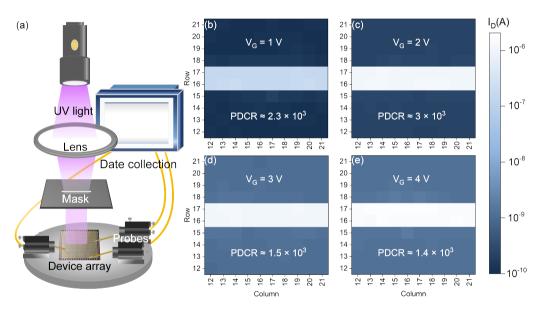

Fig.C2(a) shows the array imaging system composed of a UV light source, lens, mask and data collection system. The 254 nm UV beam illuminates a 0.4 mm wide strip spot pattern on the array through the mask. Fig.C2(b-e) show the imaging results of 10 × 10 pixels of array of different V<sub>G</sub> under V<sub>D</sub> = 2 V. The imaging results show a non-monotonic trend in the PDCR with increasing V<sub>G</sub>. When V<sub>G</sub> = 1 V, the PDCR is approximately 2.3 × 10<sup>3</sup>. When V<sub>G</sub> = 2 V, the PDCR improves to 3 × 10<sup>3</sup>. However, when V<sub>G</sub> continues to increase to 3 V and 4 V, PDCR decreases to about 1.5 × 10<sup>3</sup> and 1.4 × 10<sup>3</sup>, respectively. The imaging results obtained at V<sub>G</sub> = 2 V exhibit superior clarity compared to other V<sub>G</sub> conditions. This phenomenon can be attributed to the effective regulation of the gate voltage on the conductive channel state. Signal-to-noise ratio (SNR) can characterize the intensity ratio of the useful signal to the background noise. Based on the discussion above, a moderate V<sub>G</sub> can enhance the photo-generated carrier concentration while to suppress the dark current, which can also improve SNR significantly.

Figure C1 Energy band diagram of gate oxide layer and  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> film under V<sub>G</sub> < 0.

Figure C2 (a) Schematic of imaging system; Comparison of imaging results with different  $V_G$  under P of 1250  $\mu$ W/cm<sup>2</sup> under  $V_D = 2$  V; (b)  $V_G = 1$  V; (c)  $V_G = 2$  V; (d)  $V_G = 3$  V; (e)  $V_G = 4$  V.