# SCIENCE CHINA Information Sciences

October 2021, Vol. 64 201401:1-201401:33 https://doi.org/10.1007/s11432-021-3235-7

• REVIEW •

# Recent progress of integrated circuits and optoelectronic chips

Yue HAO<sup>1\*</sup>, Shuiying XIANG<sup>1,2\*</sup>, Genquan HAN<sup>1</sup>, Jincheng ZHANG<sup>1</sup>, Xiaohua MA<sup>1</sup>, Zhangming ZHU<sup>1</sup>, Xingxing GUO<sup>2</sup>, Yahui ZHANG<sup>2</sup>, Yanan HAN<sup>2</sup>, Ziwei SONG<sup>2</sup>, Yan LIU<sup>1</sup>, Ling YANG<sup>1</sup>, Hong ZHOU<sup>1</sup>, Jiangyi SHI<sup>1</sup>, Wei ZHANG<sup>3</sup>, Min XU<sup>4</sup>, Weisheng ZHAO<sup>5</sup>, Biao PAN<sup>5</sup>, Yangqi HUANG<sup>6</sup>, Qi LIU<sup>7</sup>, Yimao CAI<sup>8</sup>, Jian ZHU<sup>9</sup>, Xin OU<sup>10</sup>, Tiangui YOU<sup>10</sup>, Huaqiang WU<sup>11</sup>, Bin GAO<sup>11</sup>, Zhiyong ZHANG<sup>12</sup>, Guoping GUO<sup>13,14,15</sup>, Yonghua CHEN<sup>16</sup>, Yong LIU<sup>17</sup> Xiangfei CHEN<sup>18</sup>, Chunlai XUE<sup>19,20</sup>, Xingjun WANG<sup>21</sup>, Lixia ZHAO<sup>22</sup>, Xihua ZOU<sup>23</sup>, Lianshan YAN<sup>23</sup> & Ming LI<sup>19,20,24</sup>

<sup>1</sup>School of Microelectronics, Xidian University, Xi'an 710071, China;

<sup>2</sup>State Key Laboratory of Integrated Service Networks, Xidian University, Xi'an 710071, China;

<sup>3</sup>National Integrated Circuit Innovation Center, Shanghai 201203, China;

<sup>4</sup>School of Microelectronics, Fudan University, Shanghai 200433, China;

<sup>5</sup>National Integrated Circuit Innovation Center, Shanghai 201203, China;

<sup>6</sup>School of Integrated Circuit Science and Engineering, Beihang University, Beijing 100191, China;

<sup>7</sup>Frontier Institute of Chip and System, Fudan University, Shanghai 200433, China; <sup>8</sup>Institute of Microelectronics, Peking University, Beijing 100871, China;

<sup>9</sup>Nanjing Electronic Devices Institute, Nanjing 210016, China;

<sup>10</sup>State Key Laboratory of Functional Material for Informatics, Shanghai Institute of

Microsystem and Information Technology, Chinese Academy of Sciences, Shanghai 200050, China;

<sup>11</sup>Institute of Microelectronics, Tsinghua University, Beijing 100084, China;

<sup>12</sup>Center for Carbon-based Electronics, Department of Electronics, Peking University, Beijing 100871, China;

<sup>13</sup>CAS Key Laboratory of Quantum Information, University of Science and Technology of China, Hefei 230026, China;

<sup>14</sup>CAS Center for Excellence and Synergetic Innovation Center in Quantum Information and Quantum Physics,

University of Science and Technology of China, Hefei 230026, China;

<sup>15</sup>Origin Quantum Computing Company Limited, Hefei 230026, China;

<sup>16</sup>Key Laboratory of Flexible Electronics & Institute of Advanced Materials, Nanjing Tech University, Nanjing 211816, China;

<sup>17</sup>State Key Laboratory of Electronic Thin Films and Integrated Devices, School of Optoelectronic Science and Engineering,

University of Electronic Science and Technology of China, Chengdu 610054, China;

<sup>18</sup>National Laboratory of Solid State Microstructures & College of Engineering and Applied Sciences,

Nanjing University, Nanjing 210093, China;

<sup>19</sup>State Key Laboratory on Integrated Optoelectronics, Institute of Semiconductors, Chinese Academy of Sciences,

Beijing 100083, China;

<sup>20</sup>Center of Materials Science and Optoelectronics Engineering, University of Chinese Academy of Sciences,

Beijing 100049, China;

<sup>21</sup>State Key Laboratory of Advanced Optical Communication Systems and Networks, School of Electronics Engineering and Computer Science, Peking University, Beijing 100871, China;

<sup>22</sup>School of Electrical and Electronic Engineering, Tiangong University, Tianjin 300387, China;

<sup>23</sup>Center for Information Photonics and Communications, School of Information Science and Technology,

Southwest Jiaotong University, Chengdu 611756, China;

<sup>24</sup>School of Electronic, Electrical and Communication Engineering, University of Chinese Academy of Sciences,

Beijing 100049, China

Received 9 February 2021/Revised 26 March 2021/Accepted 30 March 2021/Published online 27 May 2021

© Science China Press and Springer-Verlag GmbH Germany, part of Springer Nature 2021

<sup>\*</sup>Corresponding author (email: yhao@xidian.edu.cn, syxiang@xidian.edu.cn)

**Abstract** Integrated circuits (ICs) and optoelectronic chips are the foundation stones of the modern information society. The IC industry has been driven by the so-called "Moore's law" in the past 60 years, and now has entered the post Moore's law era. In this paper, we review the recent progress of ICs and optoelectronic chips. The research status, technical challenges and development trend of devices, chips and integrated technologies of typical IC and optoelectronic chips are focused on. The main contents include the development law of IC and optoelectronic chip technology, the IC design and processing technology, emerging memory and chip architecture, brain-like chip structure and its mechanism, heterogeneous integration, quantum chip technology, silicon photonics chip technology, integrated microwave photonic chip, and optoelectronic hybrid integrated chip.

**Keywords** integrated circuit, semiconductor science and technology, optoelectronic device and chip, photonic integrated circuit, wide bandgap semiconductors, silicon photonics, hybrid integration, quantum chip, integrated microwave photonic, photonic neural computing

Citation Hao Y, Xiang S Y, Han G Q, et al. Recent progress of integrated circuits and optoelectronic chips. Sci China Inf Sci, 2021, 64(10): 201401, https://doi.org/10.1007/s11432-021-3235-7

## 1 Introduction

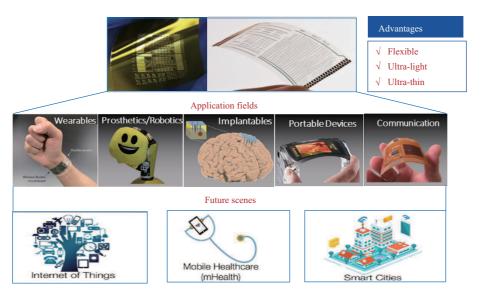

One of the significant technological achievements of the last 60 years is the integrated circuit (IC). Nowadays, the IC industry is closely related to everyone's daily life, as shown in Figure 1. With the rapid development of the computer, Internet, mobile communication, big data, cloud computing, artificial intelligence (AI), 5G communication, optical communication, Internet of things (IoT), automotive electronics, satellite, quantum information, and other emerging technology applications, the demand for IC has been explosively increased in recent years. In particular, due to the COVID-2019, there are new consumption scenarios such as intelligent conferences, remote intelligent medical systems, and online education. These applications call for high-performance computing, low transmission delay, and low power consumption.

Semiconductor science and technology are the foundation stones of the IC industry [1]. The IC products, such as the information transmission and processing devices and chips, are made of semiconductor materials. The first-generation semiconductor materials are represented by Si and Ge. The silicon devices and ICs account for the majority of all semiconductor products, which lead to the rapid development of microcomputers. The second-generation semiconductor materials are represented by GaAs and InP. With these compound semiconductor materials, the semiconductor lasers with wavelengths at 850, 1310, and 1550 nm that match well with the low loss windows of optical fiber, are the foundation of the optical communication network. Thus, optical communication chips have become an indispensable part of the communication industry. Besides, the wide bandgap (WBG) third-generation semiconductor materials represented by SiC and GaN have broad application prospects in the fields of light display, light storage, and light illumination [2,3]. The GaN is especially suitable for high frequency, high efficiency, high temperature, high voltage, and wideband high power microwave devices, which are promising candidates for radar detection, satellite communication, and 5G communication. Furthermore, the ultra-wide bandgap semiconductor materials represented by  $Ga_2O_3$  and AlN have also attracted extensive attention in recent years [4,5]. Various semiconductor devices and ICs promote the rapid development of modern information society. Every electronic product we touch may contain at least one semiconductor chip. An example is a mobile phone, which contains Si and GaAs components.

Since complementary metal-oxide semiconductor (CMOS) technology was born in the 1950s, the IC industry has been driven by the so-called "Moore's law". In 1965, Gordon Moore predicted that the number of components per chip would continue to increase by a factor of two every year, and conversely, the size of each transistor would decrease continuously [6]. In 1975, Moore updated his earlier prediction by forecasting that components per chip would double every two years [7]. In 1965, the minimum feature size of the IC chip was approximately 50 mm. The device dimension of the CMOS transistor has been scaled continuously [8]. The progression of semiconductor scaling is marked by technology nodes [9]. Traditional metal-oxide-semiconductor field-effect transistors (MOSFETs) scaling worked well up until the 130-nm generation in the early 2000s. After that, significant innovations in transistor materials and structure were introduced to continue scaling. An example was the introduction of strained silicon transistors on Intel's 90-nm technology in 2003. As another example, high-K metal gate transistors were introduced on Intel's 45-nm technology in 2007. The next major innovation was the introduction

Figure 1 (Color online) Representative applications of ICs.

of FinFET transistors on Intel's 22-nm technology in 2011. Since then, FinFET has involved in five generations of evolvement as predicted by Moore's law and typically progresses as 22, 14, 10, 7, 5, 3 nm. These innovations have continuously improved the IC performance.

Unfortunately, the device downscaling trend is now much slowing down owing to the power limitations and quantum effects. The feature size has approached the technological and physical limits. Note that, as the feature size of the transistor becomes smaller and meanwhile as billions of transistors are integrated into one chip, both the leakage currents induced static power and Joule heat-induced dynamic power are challenging problems. Simultaneously, quantum tunneling effect and matter-wave characteristics will make the transistor extremely unreliable [10]. In addition, design and fabrication cost greatly block the technological evolution. Therefore, it is difficult to further improve the computing performance by relying solely on transistor miniaturization.

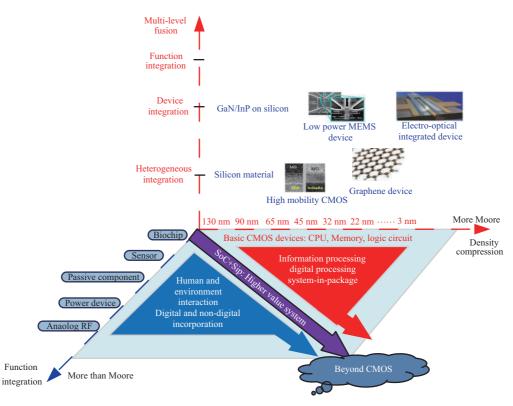

At present, IC has entered the post Moore's era from the "Moore's law era". As shown in Figure 2, "More Moore", "More than Moore", and "beyond-CMOS" are three main development directions [11,12]. For instance, FinFETs with new materials and new structures have been developed as a "More Moore" technology. The possibility to realize the diversification of functionalities of CMOS circuits by integration with other technologies has been referred to as "More than Moore". The "More than Moore" approach allows for incorporating digital and non-digital functionality, e.g., power control, analog circuits, radio frequency (RF) circuits, passive components, sensors, and actuators, into compact systems with the system on chip (SoC) or system in package (SiP) technologies. An example that has witnessed considerable commercial success is provided by CMOS imagers which can be found in any cell phone camera. The optical sensors based on Si photodetectors or phototransistors are monolithically integrated on a CMOS chip. Besides, the integration of different technologies, for instance, Si and III-V semiconductors, is also appealing. For example, optical passive components can be fabricated with Si technology, which could provide guiding, routing, and other optical functionality directly on chip. Light sources can be fabricated with compound semiconductors like GaAs and InP. These chips fabricated with different technologies can be further integrated with three-dimensional (3D) or heterogeneous integration technology, which can take advantage of the integration density of Si CMOS and the superior performance of non-Si devices or components.

Meanwhile, optoelectronic technology is an important branch of electronic information technology. Significant achievements have been made in optoelectronic technology and industry. Optoelectronic devices and integration technology have many obvious advantages, such as low power consumption, high speed, and wide bandwidth. They are widely used in optical communication, sensing, computing, displaying, and illumination. At present, photonic integrated circuit (PIC) mainly relies on different integrated material systems, such as III-V group, silicon-based, silicon nitride/silicon dioxide, lithium niobate (LN) material to realize chip integration. According to different functionalities, distinct material systems are required. The coexistence of multiple material systems will become the state of optoelectronic integration

Hao Y, et al. Sci China Inf Sci October 2021 Vol. 64 201401:4

Figure 2 (Color online) A roadmap for IC development in the post Moore's era [11].

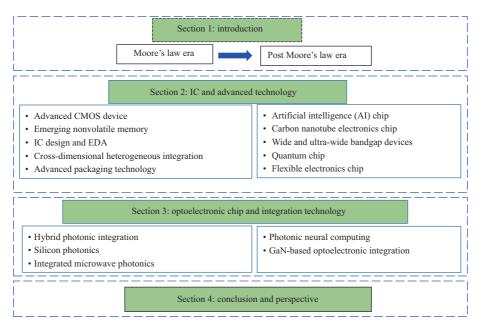

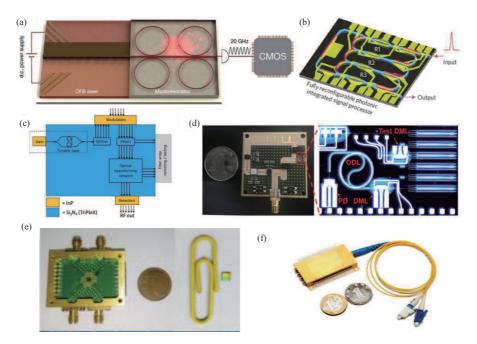

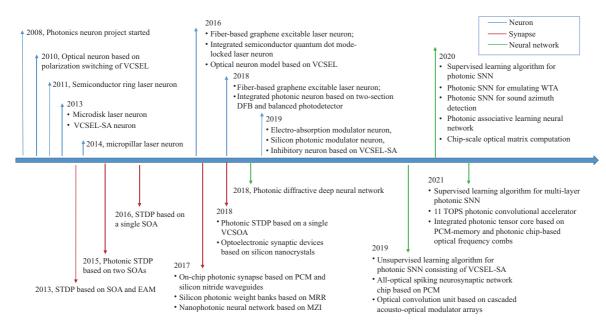

technology for a long time in the future. How to realize the system integration of multiple material systems and multiple functional devices needs to be solved, which is quite different from the microelectronic IC technology. The advanced IC and optoelectronic chips are the key foundations to further promote high-performance computing chips and transmission chips. In recent years, many innovative devices, chips, and integration technologies have been developed to further increase the IC performance. Herein, we review the recent progress of the IC and optoelectronic chips in China and abroad. The research status and development trend of devices, chips and integrated technologies of typical IC and optoelectronic chip are focused on. The organization of this paper is shown in Figure 3. In Section 2, we focus on the typical IC technologies and chips. The main contents include the advanced CMOS device and technology in the post Moore's era, emerging memory and chip architecture, IC design and electronic design automation (EDA) technology, cross-dimensional heterogeneous integration, AI chip and brain-like chip, carbon nanotube (CNT) electronic chip, wide and ultra-wide bandgap devices, quantum chip technology, and flexible electronics chip (FEC). In Section 3, we present the advances of the optoelectronic chip and integration technology. The hybrid photonic integration technology, silicon photonics, microwave photonic chip, photonic neural computing technology, and GaN-based optoelectronic integration are discussed. Finally, we summarize the challenges and opportunities faced by IC and optoelectronic chips, and propose promising solutions and perspectives.

# 2 Typical IC technologies and chips

## 2.1 Advanced CMOS device and technology

As predicted by "Moore's law", with the downsizing of the devices, the chip is expected to achieve better PPAC (performance, power, area, and cost) than the prior node. However, these aggressive scaling targets have become more and more difficult to achieve at advanced technology nodes with numerous new challenges arising [13–15]. From the transistors perspective, referred to as 'front end of the line' (FEOL), the challenge is to overcome the short channel effects (SCE), i.e., the difficulty to effectively turn off the transistors of nanometer-scale gate lengths, and to boost the transistor drive current simultaneously. Over the past 20 years, emerging technologies, such as strain Si technology, high-K metal gate technology,

Hao Y, et al. Sci China Inf Sci October 2021 Vol. 64 201401:5

Figure 3 (Color online) Organization of this paper.

and FinFET technology have been widely adopted in mainstream CMOS manufacture to maintain the CMOS scaling. From the interconnect perspective, referred to as 'back end of the line' (BEOL), the challenge is to control the RC delay from the more and more sophisticated wiring. Technologies like advanced silicide, novel lower resistivity metal materials, and low-K dielectric are widely adopted into the advanced CMOS platform.

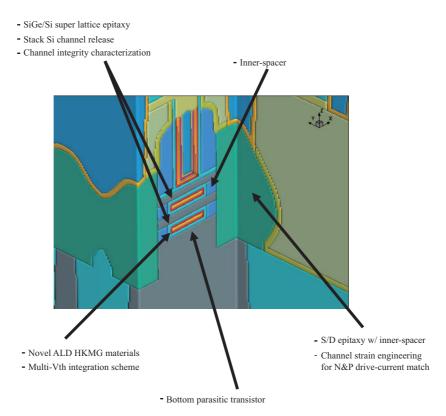

To maintain a profitable PPAC scaling, several key innovations should be explored and implemented in the advanced CMOS technology. With gate length down to 12–15 nm at 3 nm technology node and beyond, the SCE becomes out of control and FinFET does not have good capability to turn off the channel underneath the Fin, causing significant degradation of subthreshold swing (SS > 75 mV/dec) [14]. Besides, beyond 5 nm technology node, the Fin aspect-ratio will be larger than 10:1, which can cause Fin bending and eventual collapse. For continuing CMOS technology scaling down, gate-all-around (GAA) transistor will replace FinFET as the mainstream [16]. The new device architecture requires a lot of innovations before putting into production, such as channel formation, inner-spacer, gate stacks, novel channel strain engineering, and some unique characterizations of channel integrity and channel strain evolution along with the process flow. Tremendous efforts have been spent to overcome all the above challenges for the production of GAA CMOS technology beyond 3 nm, as shown in Figure 4.

Furthermore, to consider the continuing development of the GAA technology, 3D integration and twodimensional (2D) material logic technology have to be intensively explored [17]. As the IC technology continuously scales down to 3 nm node and beyond, vertically integrated devices such as vertical nanowire transistors and complementary FET will show the potential in high density, low cost, and low power after lateral GAA technology. Besides the device-level vertical integration, the monolithic 3D integration or 3D sequential integration (3DSI) is a more effective way to build high density and high energy-efficient computing systems [18]. The main challenge for 3DSI is the thermal budget which not only affects the reliability of bottom devices but also limits the quality of top devices. 3DSI has provided new opportunities in boosting the high-performance computing, energy-efficiency computing along the "More Moore" route while cost reduction and smart sensor along with the "More than Moore" road. 3DSI also provides a lot of room for scientific exploration in materials, algorithms, architectures, and even ecosystems.

Benefit from the reduction of spatial dimensions, 2D semiconductors can break the quantum confinement in bulk materials, and are expected to provide high-performance, low-power computing at the sub-3 nm technology node. Moreover, taking advantage of low temperature processes and van der Waals (vdW) integration of 2D materials, low-cost BEOL integration with current technology shows unparalleled advantages and potential of commercialization [14].

From the process perspective, the main challenges focus on advanced photolithography technology,

Figure 4 (Color online) The key technology challenges for GAA transistor implementation.

suppression of parasitic resistance and capacitance, and control of reliability and its modeling. For future advanced CMOS technology development, a joint design-technology co-optimization plays a pivot role in the pathfinding of appropriate device, layout, and process integration to meet the profitable PPAC scaling, with much better efficiency and lower cost [19].

## 2.2 Emerging nonvolatile memory: devices and chips

In conventional von Neumann computing architecture, the processing unit and the memory unit are physically separated, and data communication between the two components relies on a data bus with limited bandwidth. The data communication results in bottlenecks in computing performance and power consumption. Particularly, in the era of big data-driven AI, data communication is more frequent and the amount of data that needs to be stored and processed is far greater than before. The "von Neumann bottleneck" is becoming more prominent with the explosive growth of data volume.

As a result, the search for a good memory medium that supports such an integration of data storage and processing in a single die has been accelerated in the field of microelectronics. In this context, emerging nonvolatile memory (NVM) technologies, such as resistive RAM (RRAM), phase-change memory (PCM), and magnetic RAM (MRAM), have attracted considerable attention in academia and industry [20–22]. Mainstream IC companies, e.g., Intel, Samsung, TSMC, and IBM, and several startups, e.g., Crossbar and Avalanche are involved in the development of these nonvolatile memories. As can be seen from Figure 5(a) [23], RRAM devices comprise metal-insulator-metal (MIM) stacks, and the resistive switching process typically involves the creation and disruption of conductive filaments (CF) comprising a localized concentration of defects. A low resistance state (LRS) corresponds to CFs bridging the two metal layers. Even though the history of RRAM can be traced back to at least the 1960s [24], key technological demonstrations in the 2000s [25] gave significant impetus to this technology. PCM, which also dates back to the 1960s [26], is based on the property of certain types of materials, such as  $Ge_2Sb_2Te_5$ , to undergo a Joule heating-induced, rapid and reversible transition from a highly resistive amorphous phase to a highly conductive crystalline phase [27]. As shown in Figure 5(b), a typical PCM device has a mushroom shape where the bottom electrode confines heat and current. This results in a near-hemispherical shape of the amorphous region in the high resistance state (HRS). By crystallizing the amorphous region, the LRS state is obtained. MRAM is a product of spintronics, which manipulates the spin freedom in addition to

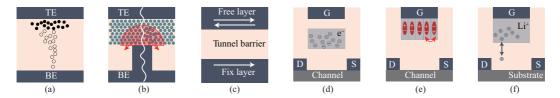

Figure 5 (Color online) (a)–(c) Two-terminal NVM devices. (a) An RRAM device in the LRS where the CF comprises a large concentration of defects for example oxygen vacancies in metal oxides or metallic ions injected from the electrodes. (b) A mushroom-type PCM device in the HRS state where the amorphous phase blocks the bottom electrode. (c) An STT-MRAM device with two ferromagnetic layers (pinned and free) separated by a tunnel oxide layer. (d)–(f) Three-terminal NVM devices: flash memory (d), FeRAM (e), and ECRAM (f). The FeRAM device (e) utilizes the partial polarization switching within the ferroelectric gate oxide to change conductance. The conductance tuning of an ECRAM device (f) is based on the motion of Li ions between the solid-state electrolyte and tungsten oxide. Reprinted with permission from [23] @Copyright 2020 Nature Publishing Group.

the charge of electrons to carry and process information [28]. An MRAM cell consists of a magnetic tunnel junction (MTJ) structure with two ferromagnetic metal layers (pinned and free), which could be made of the CoFeB alloy and thin tunnel oxide such as MgO (Figure 5(c)). In the pinned layer, the magnetic polarization is structurally fixed to act as a reference, whereas in the free layer it is free to change during the write operation. Voltage pulses of opposite polarities are applied to switch the polarization of the free layer. Depending on whether the two ferromagnetic polarizations are parallel or anti-parallel, the LRS and HRS states are obtained due to the tunnel magnetoresistive effect [29].

The abovementioned three NVMs are among the most promising candidates for mass production, especially the Spin transfer torque MRAM (STT-MRAM), which stores information in the magnetization of a nanoscale magnet. The STT-MRAM has attracted wide attention owing to its low power consumption and high performance, and STT-MRAM chip demonstrations have advanced significantly in recent years. Standalone STT-MRAM products became commercially available in 2015 with a 64-Mb part [30]. Subsequently, leading semiconductor industries and tool suppliers have aggressively launched their development programs for STT-MRAM in terms of either eFlash or SRAM replacement. For example, Intel announced NOR-Flash replacement, while Samsung and Everspin/GF announced the release of a 1 Gb STT-MRAM on the 28 nm node [31]. Besides STT-MRAM, RRAM, and PCM operate based on the rearrangement of atomic configurations and hence have worse access times (write speed) and cycling endurance than MRAM. However, they have substantially larger resistance windows that enable the storage of intermediate resistances even at an array level. RRAM has the advantage of using materials that are common in semiconductor manufacturing. Despite the simplicity of the device concept, a comprehensive understanding of the switching mechanism is still lacking compared to PCM and MRAM.

Other candidates that are approaching commercialization include Ferroelectric RAM (FeRAM) [32] and electrochemical random-access memory (ECRAM) [33] as shown in Figures 5(d)-(f). Three-terminal NVM devices provide better control of conductance tuning capability through the modulation from an additional gate terminal. In comparison, flash memory (Figure 5(d)) is the most mature NVM technology. The main challenge regarding flash memory technology for computing applications lies in its slow programming speed, which significantly increases the learning energy. FeRAM (Figure 5(e)) has gained attention due to its faster speed, lower programming voltage, and nearly symmetric channel conductance tuning ability using carefully designed programming schemes [34]. Very recently, a lot of emerging electrochemical synaptic devices have been developed (Figure 5(f)), showing excellent analog conductance tuning performance.

Novel NVM devices which store information using different physical mechanisms offer a unique opportunity to bring large amounts of memory closer to the computing elements, resulting in high-bandwidth, low-latency access. The in-memory computing is an appealing technique that can break through the "memory wall". With the ability to tightly integrate massive amounts of memory with logic, it is conceivable that future computing chips may be much more compact and energy-efficient.

## 2.3 IC design: AI and IC design, ADC, millimeter-wave and THz IC

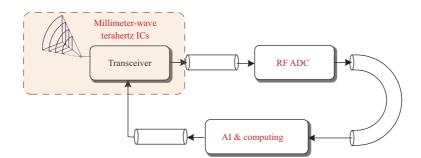

The AI chip and high-performance computing, ultra-high speed analog-to-digital converter (ADC) and millimeter-wave (MMW) and terahertz (THz) ICs are hotspots and in short-needed technologies for high-tech developments as shown in Figure 6.

Figure 6 (Color online) The key ICs of high-performance electronic and communication systems.

#### 2.3.1 Chip design for AI high-performance computing

In the era of AI, IC is experiencing rapid transformations prompted by the increasing amount of calculation and applications of AI in the field of the chip design. With the rapid development of AI, the computation power of traditional devices like CPU and GPU can hardly keep pace with the development of algorithms such as accelerated computing of deep neural networks demanded by AI applications. This brings challenges to the chip design. Meanwhile, the application of AI in the field of chip design also brings new opportunities for chip development.

For the purpose of eliminating the performance limit of the von Neumann architecture, one solution to realize a better AI accelerator chip design is to make it more brain-like [35]. One example would be the TrueNorth chip invented by IBM in 2015. It integrates 5.4 billion silicon transistors to form 4096 physical cores. The processing capacity of the TrueNorth is equivalent to a supercomputer [36]. Intel has also released a brain-like chip named "Intel Loihi", which applied a neural mimic calculation method imitating the principle of the human brain [37]. It has an asynchronous circuit that uses an asynchronous spiking neural network (SNN), and therefore eliminates the usage of a global clock signal. Intel claims that Loihi is up to 1000 times faster than traditional CPUs and is up to 10000 times more energy efficient in specific applications such as sparse coding, schema search, simultaneous positioning and mapping, and constraint satisfaction problems. Although there are some examples of brain-like chips, it still has a long way to go before putting the brain-like chips into practical applications.

In addition, to improve chip performance from an architectural perspective, the chiplet is also a good choice for improving performance in other aspects in recent years [38]. By integrating cores of different architectures, chiplet does not only lower the cost, but also helps to reduce the power density.

Overall, to meet the ever-increasing need for AI computing ability, the design of ICs has three directions to explore. Firstly, we can customize the neural network accelerator according to the different characteristics of the neural network, which can bring high performance to the specific algorithm. Secondly, we may give up the traditional von Neumann architecture, and turn the eyes to the brain-like chip architecture. Thirdly, a new packaging technology like chiplet can be adopted.

To get a promising performance under specific network accelerators, designers will need to do a fullstack optimization rather than keep eyes merely on the chip design or algorithm research. The optimization of each individual stage of AI chip design and manufacturing is gradually approaching its threshold, and requires joint optimization at all stages, such as the construction of the low-level AI development environment, the design concept of the fully self-developed AI computing framework, and the development of the full scene AI application. Furthermore, with the regularization of AI chips, full-stack optimization is now possible in the field of AI chips. To fully tap into the accelerator's potential, designers must take into account the software features while designing the hardware.

#### 2.3.2 AI application in chip design and architecture

Not only is the chip designed to meet the requirements of the AI computation market, AI also plays a more and more important role in the domain of IC design. For instance, there are a lot of problems in the 5G system that are yet to be solved, including the network self-organization and self-optimization and time-frequency optimal allocation. These problems can be easily solved using AI techniques [39]. Furthermore, 6G can be transformative and will revolutionize the wireless from 5G's "connected things" to "connected intelligence". One key feature of 6G will be its ability to exploit a flexible subnetwork-wide evolution to effectively adapt to the local environments and user demands, thereby resulting in a

"network of subnetworks". In fact, in the white paper of Samsung, Samsung clearly proposed that each 6G component used the AI technology to optimize the overall system performance and network operation. Using AI modules inside a chip to obtain high performance and the low energy consumption is also a promising trend to develop AI chips.

#### 2.3.3 IC design law for ultra-high speed ADC

Applications like wireless communications and Ethernet networks are in great demand for ultra-highspeed ADCs (or RF ADCs) [40–43]. Both academia and industry paid extensive efforts to promote the development of RF ADCs in the past decades from the following three aspects. The first one is to improve the ADC sampling speed by interleaving more channels. For example, Fujitsu released 256-channel timeinterleaved ADC recently, which achieved 56–72 GS/s with an 8-bit resolution. The second one is to use compound track and hold amplifier (THA) or heterogeneous integration of ADC core to achieve high bandwidth. Third, the continuous forward finer CMOS process makes it possible to realize RF ADC with high resolution and low power, since it allows significant digital signal processing to be integrated on the chip. In 2020, ADI reported a 12-bit 18 GS/s RF ADC with 16 nm FinFET.

The main technical challenges of high-speed RF ADCs are as follows. (1) As the process scales down, the lower power supply decreases the voltage headroom for the analog circuit design. Thus, the signal-noise-ratio (SNR) of the RF ADC becomes smaller. (2) Although the smaller gate length and feature size of the CMOS transistor makes the digital gates get faster and smaller, it lowers the transistor intrinsic gain and results in a large error and precision degradation in the analog domain. (3) The increasing of device mismatch worsens the linearity and exacerbates the distortion. (4) The analog signal bandwidth is limited not only by devices but by metal interconnection lines. This issue becomes worsen in RF ADCs with several tens of GS/s. (5) Clock jitter should be even less than several femtoseconds in RF ADCs to achieve high SNR, which requires higher accuracy and reliability of clock generation systems.

For the ADC designers, there are two possible ways to further improve the RF ADC performance and break the technology limitation. One is optimizing the performance from the circuit level. For example, using a fast and low-power dynamic amplifier instead of the conventional power-hungry operational amplifier when designing pipeline ADCs. Other circuit design techniques such as high-order dynamic element matching and advanced background calibration can also help to improve the RF ADC performance. The other way is developing novel ADC architectures from a system level. Hybrid architectures like time-domain RF ADCs can take full advantage of technology scaling down and improve the ADC power efficiency. Besides, micro-system integration is a promising trend of RF ADCs, which combines compound high bandwidth THA and silicon ADC core to achieve both high sampling speed and high bandwidth.

#### 2.3.4 Millimeter-wave and THz integrated circuits

MMW and THz frequency bands have a large number of potentially underutilized spectrum resources and have the potential to achieve ultra-high-speed communications, radars, electronic warfare, and other applications. Owing to the unique low cost and high integration of the silicon-based technology, researchers began to investigate the silicon-based MMW and THz ICs.

In 2008, Seok et al. [44] reported a 410 GHz voltage-controlled oscillator based on a 45 nm CMOS process demonstrated with a push-push structure. This work was the first reported silicon-based THz source in the THz frequency band, but its output power was very small, only -47 dBm (20 nW). In 2012, Sengupta et al. [45] demonstrated a 4×4 array of 280 GHz source based on the 45 nm CMOS process, with the output power reaching 1 dBm. After that, Afshari et al. [46,47] did a series of research on silicon-based THz oscillators from 200 to 500 GHz. In 2017, Meng et al. [48] proposed an oscillator design method and realized a 193 GHz voltage controlled oscillator.

The earliest exploration of silicon-based THz transceiver systems mainly adopted on-off keying (OOK) modulation, which requires the lowest clock jitter performance. In 2012, Park et al. [49] adopted a quadrupler-based architecture to implement an OOK-modulated silicon-based THz transceiver that operated at 260 GHz based on harmonics, with a data rate of 10 Gbps, and the power consumption exceeded 1 W. Aiming at the problems of low gain, low output power and low efficiency of the harmonic-based THz transceiver system architecture, in 2013, Wang et al. [50] proposed an OOK-modulated silicon-based THz transceiver based on the fundamental frequency and working at 210 GHz. In 2015, Deng et al. [51] reported a 320 GHz OOK transmitter based on a 0.13 µm SiGe BiCMOS process.

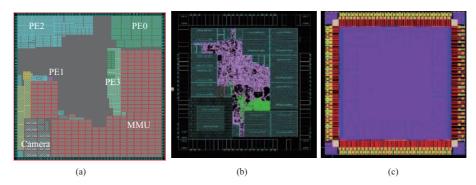

Figure 7 (Color online) (a) Aerospace level chip layout; (b) chip layout of RISCV; (c) signal processing chip layout.

The current progress on the MMW and THz ICs has demonstrated the great potential of silicon-based ICs at high frequency. However, there are still huge challenges for the design of MMW and THz ICs. (1) The silicon-based transistor model provided by the CMOS foundry is not suitable for the MMW and THz frequency band. (2) The output power and power-added efficiency of silicon-based THz frontend amplifiers are low. (3) The phase noise problem of the silicon-based THz local oscillator frequency source plays an important role in the transmission quality of the signal in terms of the error vector magnitude (EVM). The EVM will significantly deteriorate with the increase of carrier frequency and the modulation order. The above technical challenges make the current THz IC design very difficult, and traditional design methods are no longer applicable. Facing these difficulties and challenges, it is necessary to conduct in-depth research in terms of models, circuits, systems, in terms of THz transistor noise model/large-signal model, near-fmax design methodology, high-gain THz amplifier, low-jitter THz source, THz phased array, and low-loss THz chip interconnection technology to make breakthroughs to prompt the development of new spectrum technologies.

#### 2.4 EDA technology

The EDA is the foundation and tool for the development of the IC industry [52–54]. More specifically, EDA aims to realize the automatic design of electronic products with a computer platform, by integrating electronic technologies, computer technologies, information processing technologies, and intelligent technologies. EDA has completely transformed the way of designing and manufacturing ICs. With EDA, the circuit design, performance analysis, IC layout design, printed circuit board (PCB) layout design, and back-end verification of electronic products are realized by using a computer software platform. For instance, EDA has been successfully applied in circuit design from the first microprocessor (Intel 4004), with 2250 transistors, to the latest multicore processor, with over a billion transistors. Figure 7 shows some chip layouts designed with EDA by researchers from Xidian University.

The development of EDA can be divided into four stages. In the computer aided design (CAD) stage in the 1970s, the computer-aided IC layout editing, PCB layout and wiring were adopted to replace the manual operation. The 1980s was referred to as the stage of computer aided engineering (CAE). Different from CAD, CAE not only has drawing function, but also can realize circuit function design and structure design. With the help of electrical connection netlist, the engineering design can be realized. The main functions of CAE include the schematic input, logic simulation, circuit analysis, automatic layout and wiring, and PCB post analysis. The 1990s corresponds to the EDA stage. The design abstract level was promoted to the language level. The language description can be automatically transformed into circuit through EDA tools, which can greatly improve the design efficiency. The key process is synthesis, namely, transforming hardware description language (HDL) into circuit netlist and layout. Since the 21st century, EDA technology has been further abstracted and systematized, and gradually evolved to electronic system level (ESL) [1].

With the rapid development of the AI technology, the IC design methodology has undergone a subversive change, from the traditional "aided" design methodology based on the analysis and optimization technology to the "intelligent" design methodology based on data-driven machine learning. It is believed that, the realization of intelligent and agile design of ICs through AI and machine learning is the future development trend of IC design methods and tools.

Hao Y, et al. Sci China Inf Sci October 2021 Vol. 64 201401:11

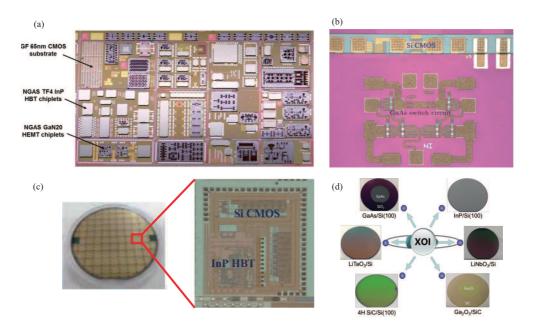

Figure 8 (Color online) Some examples of heterogeneous integration chips. (a) CMOS to III-V chiplet integration [57] @Copyright 2017 IOP Publishing. (b) GaAs pHEMT epi-layer lift-off and transferred on the silicon CMOS circuit [58] @Copyright 2016 IOP Publishing. (c) InP HBT/Si CMOS-based heterogeneous integrated circuit [59] @Copyright 2009 IOP Publishing. (d) Wafer-scale XOI heterogeneous integration materials fabricated by ion-cutting technique.

#### 2.5 Cross-dimensional heterogeneous integration

The cross-dimensional heterogeneous integration technology is a crucial method that does not completely rely on linewidth reduction. It aims to integrate different materials (InP, GaN, GaAs, SiC, Si, organic molecules, etc.), different structures, and different functions (optoelectronic, RF, sensing, biological, etc.) through interdisciplinary and multi-disciplinary integration, architecture design, fusion algorithm and micro/nano 3D integrated manufacturing process [55,56]. The chip integrated by cross-dimensional heterogeneous integration solution can take full advantages of different materials, devices, and functions, which has a smaller volume, lighter weight, higher performance, and more functions. The key point of cross-dimensional heterogeneous integration is to break through the three integration levels in materials, devices and system functions. Combining the elements of microelectronics, optoelectronics, microelectromechanical systems (MEMS), architectures, and algorithms via cross-dimensional heterogeneous integration with new design ideas, design methods, manufacturing methods, at the micro/nanoscale, a microsystem can be achieved with multi-functional integration of signal perception, signal processing, signaling execution and enabling. Cross-dimensional heterogeneous integration will open up a new way for the development of microelectronic technology in the post Moore's era.

The heterogeneous integration technology has been developed rapidly since the 1990s when Defense Advanced Research Projects Agency (DARPA), the US Department of Defense, first proposed the concept of heterogeneous integration. As shown in Figure 8(a), with chiplet heterogeneous integration technology, GaN, InP, and GaAs chips and MEMS high-Q components were heterogeneously integrated on silicon CMOS wafers, and the distance between heterogeneous interconnects was less than 5  $\mu$ m [57]. It takes the advantage of the high RF performance of compound semiconductors and the high integration density of CMOS circuits. Based on the epitaxial lift-off and transfer technology, the researchers realized the monolithic integration of the digital control switch circuit of GaAs PHEMT and Si CMOS as illustrated in Figure 8(b) [58]. It has been reported that InP heterojunction bipolar transistors (HBTs) can be integrated on Si materials platforms within silicon fabrication facilities [59], as presented in Figure 8(c). Based on the ion-cutting technology [60–63], the researchers realized different kinds of wafer scale heterogeneous integration materials, e.g., GaAs/Si, InP/Si, LiTaO<sub>3</sub>/Si, LiNbO<sub>3</sub>/Si, SiC/Si, and Ga<sub>2</sub>O<sub>3</sub>/SiC, as shown in Figure 8(d).

The main technical challenges of cross-dimension heterogeneous integration are as follows. (1) Crossmaterial-dimension heterogeneous integration technology may introduce the material matching, integrated manufacturing, thermal design and electromagnetic compatibility characteristics. (2) Heterogeneous integrated transmission technology across device dimensions induces transmission problems in systems of different materials, structures and functions. (3) It is still open to reveal the mechanism of the electromagnetic signal on cross-dimensional heterogeneous integration, especially the mode radiation mechanism and feed coupling mechanism of the electromagnetic signal in different materials, structures, and modules. (4) The integration technology of cross-dimension heterogeneous integrated manufacturing and its compatibility with the existing mature chip level and board level process interconnection integration technology need to be solved. (5) It is highly desirable to develop novel cross-dimensional heterogeneous integration technology design tools.

Cross-dimensional heterogeneous integration technology is one of the best solutions to realize the system with the comprehensive balance of function, performance, cycle and cost. It is a technical bridge from chip to system integration. The characteristic size of silicon-based devices mainly depends on the machining accuracy of the lithography machine, and the lithography machine with the machining accuracy beyond 14 nm has been a long-standing problem in the development of silicon-based ICs in China. Cross-dimensional heterogeneous integration makes full use of various process advantages to achieve circuit performance improvement. It is expected to realize the giant integration of quantum chips, brain-like chips, 3D memory chips, multi-core distributed memory chips, optoelectronic chips, and general-purpose computing chips, and eventually solve the power consumption bottleneck, computing power bottleneck, and function expansion of general-purpose and special-purpose chip technologies.

#### 2.6 Advanced electronic packaging technology

The electronic packaging technology plays an important role in chip performance. The basic functions of electronic packaging include signal distribution, power distribution, heat dissipation, and protection in mechanical, electromagnetic, and chemical aspects.

The typical packaging in the early stage of ICs was through-hole package, such as dual in-line package, single in-line package, and pin grid array package. Owing to the progress of PCB technology and the increase of system complexity, surface mount technology package developed rapidly [1]. In the past two decades, there have been various advanced packaging technologies [64–66], such as flip-chip (FC), multichip module (MCM), chip-scale package (CSP), 2.5D/3D integrated packaging based on through-silicon via (TSV), fan-out wafer-level package (FOWLP), fan-out panel level package (FOPLP). At present, wafer-level packaging (WLP) is used in massive manufacturing. In 3D IC, the chip technology and packaging technology are merged closer and closer together. TSV becomes the core of 3D integrated packaging. The SiP technology can be used to integrate different types of discrete devices, such as microprocessors, memory, and sensors into one package [67]. Besides, the chiplet-based technology, which merges multiple heterogeneous dies of diverse functional circuit blocks into a single package, has gained widespread attention. The chiplets prepared with distinct process nodes can be integrated through the SiP technology [68]. Therefore, SiP can provide enhanced performance and a smaller size compared to combining these components at the circuit board level. For instance, the increasing demand for mobile phones and tablets has driven the industry to 3D SiP technology, which can integrate many different functions (digital logic, memory, analog/mixed-signal) with a small form factor. The TSV technology provides an approach for implementing multifunctional integration with a higher packing density for a system in a package.

The development trend for packaging technology is driven by the continuous increase in demands for the smaller form factor, faster, high-density interconnection at cheaper cost.

#### 2.7 AI chip

The wide applications of AI and deep learning call for energy-efficient neural network training. To accelerate the calculation of the deep neural networks while minimizing the energy consumption, AI accelerators have been developed rapidly in recent years.

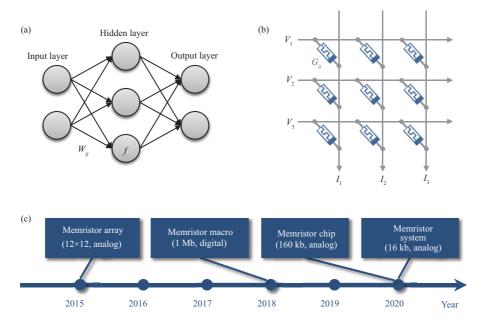

Artificial neural networks (ANNs) include artificial neurons that receive, process, and transmit signals, and artificial synapses that connect neurons and change the strength of the connection during the learning process. In Figure 9(a), the basic structure of ANN is introduced. The artificial neurons in the input layer receive the signal and propagate it to the neurons in the hidden layer. The signal is first weighted and summed through artificial synapses, then processed by the nonlinear activation function in the hidden layer, and finally propagated to the output layer. The weight of the artificial synapse  $(W_{ij})$  is adjustable during training. The core computation unit of ANN is vector-matrix multiplication (VMM). Figure 9(b)

Hao Y, et al. Sci China Inf Sci October 2021 Vol. 64 201401:13

Figure 9 (Color online) AI theory and chips. (a) The diagram of the basic structure of ANN; (b) the memristor array used for VMM; (c) the history of the memristor chips [69–72].

shows a hardware VMM unit based on a memristor array, where the calculation and storage are performed at the same location of the array. The input signal (voltage vector) is passed to each device with different conductivity, and a current is generated according to Ohm's law (I = VG, where G is the conductivity) as the calculation result. The current of each column follows Kirchhoff's law, which makes the total current of each column be the sum of currents from all the devices in the same column ( $I_j = \sum_i V_i G_{i,j}$ ). In the ANNs based on a memristor array, each memristor device is an artificial synapse. The conductance of the device can be adjusted continuously and the value can be stored for a long time. Besides, since the weights of artificial synapses may be negative and the conductance of the device is always positive, a common technique is to express the weight as the conductance difference between the two devices.

Several represented studies on memristor chips are presented in Figure 9(c). A passive  $12 \times 12$  memristor array was proposed in 2015 [69]. A simple 1 layer ANN was realized by such an array and the network can be trained in situ to perform the classification of  $3 \times 3$ -pixel black/white images into three classes. Although the passive array (no transistors in the memristor crossbar) is attractive for its potential in low power consumption, the sneak path current and half-select issues usually limit its large-scale integration. In 2018, a memristor macro with 1 Mb capacity was proposed by using 1T1R active array [70]. Although the macro can perform a convolutional neural network (CNN) with very low latency, the output of the memristor cell is only 1 bit which largely limits its performance. In 2020, a 160 kb memristor chip with a 2T2R active array was proposed [71], where 3-bit signed weight was used in one memristor cell. The chip is fully integrated for a complete multi-layer ANN and achieves 78.4 TOPS/W peak energy efficiency and 94.4% test accuracy in the MNIST dataset. The first memristor system with 8 processing elements (PEs) was proposed in 2020 [72]. Each PE chip consists of a  $128 \times 16$  memristor array and on-chip decoder circuits. The 5 layer memristor-based CNN was realized in such a system and 96.9% test accuracy in the MNIST dataset was achieved with 110 times better energy efficiency and 30 times better performance density compared with Tesla V100 GPU.

Besides, traditional volatile-memories such as SRAM and DRAM can also be used to realize in-memory computing. The core idea of SRAM based in-memory computing is equivalent to multiply-accumulate (MAC) operation by using XNOR accumulation [73, 74]. Recently, TSMC researchers have proposed an SRAM array with a high power efficiency of 89 TOPS/W which can be further improved by 19 times under a 5 nm design [75]. DRAM-based in-memory computing mainly uses the charge sharing mechanism between DRAM cells [76, 77].

In recent years, the on-chip integration of memristors has greatly developed, and some simple ANNs have been partially or fully implemented by memristor arrays. In the future, larger-scale device integration and more complex ANN implementation will be the focus of research. The high-density 3D integration will be the main technical route and one of the main challenges is to implement high-performance selectors

to eliminate sneak current paths. At the same time, the architecture and data path of the 3D large-scale memristor chips need to be carefully designed to accommodate the high bandwidth and fine-grained interconnection across multiple functional layers. In addition, the future memristor chips need to tolerate the non-ideal characteristics (such as noise and nonlinearity) of the device.

#### 2.8 CNT electronics

CNT has long been regarded as a strong replacement channel material for next-generation high performance and low power FET and IC technology beyond silicon [78], since the discovery of multi-walled CNT in 1991 [79], due to its excellent properties for application as the channel in transistors. They offer extremely high carrier mobility and saturation velocity, which in principle should provide high performance and high-speed device operation [80]. The intrinsically small body (or atomic thickness) of CNT guarantees perfect electrostatic control of carrier movement in the nanotube and they should be free of SCE. Furthermore, CNTs also offer low surface state density and have symmetric band structure (with an identical effective mass of both electrons and holes), which allows a very high gate efficiency, a low supply voltage and the potential to build symmetric CMOS.

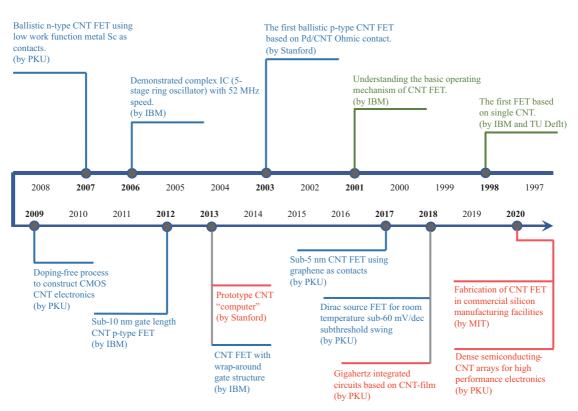

The development timeline of CNT FET and CMOS ICs with some major milestones has been summarized in Figure 10. The first FET based on CNT was reported in 1998 [81,82]. CNT FETs showed limited on-state current performance, due to the poor metal/CNT contact. The major significant break to solve the ohmic contact to CNTs was made in 2003 [83], when high work function metal palladium was used as the source and drain contact, thus leading to perfect p-type ballistic CNT FETs. In 2006, the first complex IC (5-stage ring oscillator) was successfully demonstrated and showed 52 MHz operating speed [84]. Although the p-FETs based on CNTs were approaching the performance limit, the development of n-type FET proved to be a slow and frustrating process. In 2007, another important breakthrough in the fabrication of n-type CNT FETs was made. Perfect n-type ohmic contact was observed to form between the scandium contacts and semiconducting CNTs with diameters larger than 1 nm. As a result, performance approaching that of ballistic limits was demonstrated in scandium contacted CNT FETs [85]. Based on the ohmic contact for both n-FETs and p-FETs, the polarity and performance of the CNT FETs can be easily determined by the contact of the CNT to the source/drain, instead of by the CNT channel in between the source/drain [86]. Therefore, the so-called doping-free process to construct CMOS CNT electronics was proposed in 2009 and yielded almost perfectly symmetric CMOS characteristics.

The performance limits of CNT-based CMOS have been investigated using individual CNTs. In 2017, an extremely scaled CNT CMOS FET was demonstrated. To increase the gate control on the channel, a new device structure was developed where both the source and drain were thinned down to atomic thickness (by using graphene) to reduce their electrostatic coupling to the channel. The subthreshold characteristics of the device were thus improved significantly, yielding a remarkably small subthreshold swing of 73 mV/dec at a gate length of 5 nm [87]. To further reduce the subthreshold swing to sub-60 mV/dec level, a new Dirac or cold electron source FET was developed in 2018, which offered sub-60 mV/dec subthreshold swing at room temperature and significantly reduced off-state leakage while delivering comparable on-state current at 0.5 V to that of Intel's 14-nm CMOS FETs at 0.7 V [88].

Although the prototype CNT FETs based on individual CNTs are approaching the physical limit, the requirement of scalability and integration density of devices call for the wafer-scale CNT arrays [89]. The ideal material system is well established to be aligned CNT arrays with a well-defined and consistent 5- to 10-nm pitch, a semiconducting purity estimated to be > 99.9999% [78,89]. One way to produce aligned CNT material is based on chemical vapor deposition (CVD) process followed by post-treatment. The major drawbacks of CVD processed aligned CNTs are either low CNT density resulting in poor performance or low semiconducting purity. In 2013, based on the combination of CVD-based process and post-treatment CNT arrays, researchers demonstrated a prototype "computer" that could run an operating system capable of multitasking. However, the performance of this integrated system is very low, the operating speed is only kHz, which is orders of magnitude lower than commercial silicon chips [90]. Another way of producing aligned CNTs is the solution-processed method. The major advantage of this method is its high CNT semiconducting purity, and it could provide wafer-scale assembly capability. In 2020, a method called multiple dispersion and dimension-limited self-alignment was investigated to produce extremely high semiconducting purity and well-aligned CNT arrays (within the alignment of 9 degrees) with a tunable density of 100 to 200  $\text{CNTs}/\mu\text{m}$  on a 4-inch silicon wafer. FETs based on the CNT array showed better performance than that of commercial silicon MOSFETs with similar gate

Figure 10  $\,$  (Color online) The development timeline of CNT FET and CMOS ICs.

length, and batch-fabricated top-gate 5-stage ring oscillators exhibited a highest maximum oscillating frequency of > 8 GHz [91].

CNT-based high-performance CMOS electronics have been scaled down to sub-10 nm planar nodes, and the demonstration of CNT-based ICs has shown both scalability and performance better than siliconbased 0.18  $\mu$ m CMOS. Further development of this CNT-electronics platform will require optimization of both the material preparation and corresponding device fabrication. Improvement of the uniformity of the tube-to-tube pitch, direction, and diameter of CNTs on a large scale is necessary for ultra-large-scale integration of CNT ICs, particularly for sub-10 nm technology nodes. Moreover, the CNTs in the array need to be further cleaned. At the device level, fabricating CNT CMOS FETs with standard industry processes, which are compatible with conventional CMOS processes, is an important requirement for the development of CNT-based ICs [92]. Finally, the adoption of the multilayer interconnect technology widely used in Si technology and the optimization of the device structure would also be expected to further enhance the actual potential of CNT-based technology.

#### 2.9 Wide and ultra-wide bandgap materials and devices

WBG devices provide obvious advantages for military and commercial systems due to their high output power density, high operating voltage and high input impedance. Note that, to fabricate high-power and high-frequency transistors, semiconductor materials with a large breakdown voltage (BV) and high electron velocity are desired. Table 1 lists the main parameters of GaN and other materials. Johnson's figure of merit (JM) can be calculated to compare the power-frequency limits of different materials [93]. It can be seen from Table 1 that GaN and SiC with higher JM are more suitable for making high-power and high-frequency transistors.

Thanks to the high lattice matching, high thermal conductivity, and good heat dissipation of GaN and SiC, GaN-based HEMTs (high electron mobility transistors) fabricated on SiC substrate can fully meet the requirements including high power, high efficiency and high frequency. However, the cost of SiC is always high, which slows down its commercial process. Commonly used substrate materials for GaN epitaxial growth include sapphire and silicon. Although sapphire can be produced stably at a low cost and large size, its high lattice mismatch with GaN (reaching 14) and poor thermal conductivity can affect the improvement of GaN-based devices in power density. Compared to sapphire, Si material has

|                                       | Si                   | GaAs              | H-SiC                | GaN                        | Diamond             |

|---------------------------------------|----------------------|-------------------|----------------------|----------------------------|---------------------|

| $E_g$ (eV)                            | 1.1                  | 1.42              | 3.26                 | 3.39                       | 5.45                |

| $n_i \ (\mathrm{cm}^{-3})$            | $1.5 \times 10^{10}$ | $1.5 \times 10^6$ | $8.2 \times 10^{-9}$ | $1.9 \times 10^{-10}$      | $1.6\times10^{-27}$ |

| $\varepsilon_r$                       | 11.8                 | 13.1              | 10                   | 9.0                        | 5.5                 |

| $\mu_n \ (\mathrm{cm}^2/\mathrm{Vs})$ | 1350                 | 8500              | 700                  | 1200 (bulk)<br>2000 (2DEG) | 1900                |

| $v_{\rm sat} \ (10^7  {\rm cm/s})$    | 1.0                  | 1.0               | 2.0                  | 2.5                        | 2.7                 |

| $E_{\rm br}~({\rm MV/cm})$            | 0.3                  | 0.4               | 3.0                  | 3.3                        | 5.6                 |

| $\Theta (W/cm \cdot K)$               | 1.5                  | 0.43              | 3.3 - 4.5            | 1.3                        | 20                  |

| $JM = \frac{E_{br}v_{sat}}{2\pi}$     | 1.5                  | 0.43              | 3.3 - 4.5            | 1.3                        | 20                  |

Table 1 Main parameters of GaN and other materials [4,5]

larger size, lower cost, and better thermal conductivity. Therefore, it has a larger commercial prospect.

Based on the material properties, GaN-based HEMTs have a lot of advantages over existing semiconductor technologies [94]. Owing to the higher power density, the size of GaN-based HEMTs can be greatly reduced under the same output power so that the matching of the amplifier is easier and the power loss is lower. Moreover, the ability of GaN-based HEMTs to work at high BVs can not only reduce the need for voltage conversion, but also provide the potential for high efficiency, which is a key parameter of the amplifier. Besides, the WBG also enables it to work at high temperatures. Therefore, GaN-based HEMTs are promising in high-power and high-frequency areas.

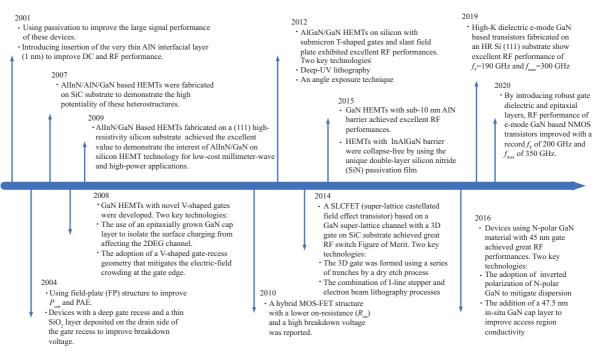

For the better application of GaN-based devices in high-power and high-frequency areas, tremendous exploratory studies have been completed ranging from material growth, device processing and device structure [95–99].

In 2004, GaN-based HEMTs on SiC with field-plate (FP) length of 1.1  $\mu$ m were reported, which achieved a continuous wave output power ( $P_{out}$ ) density of 32.3 W/mm and power-added efficiency (PAE) of 54.8% at 4 GHz [100]. This FP structure can effectively modulate the electric field distribution between the source and drain of the device and reduce the peak value of the electric field, thus increasing the BV and improving the gain and power of devices.

Except for FP structure,  $SiN_x$  passivation is also a key to improve characteristics of GaN-based devices [101]. Although  $SiN_x$  passivation can be used to reduce the dispersion, the reproducibility of BV, gate leakage, and effectiveness of dispersion elimination are strongly process-related. In 2004, a deep gate recess was used in the fabrication of GaN-based devices to achieve the desired transconductance and a thin SiO<sub>2</sub> layer was deposited on the drain side of the gate recess to reduce gate leakage current and improve BV. A BV of 90 V was achieved without a surface passivation layer. A record Pout density of 12 W/mm with an associated PAE of 40.5% were measured at 10 GHz [102].

In 2010, a hybrid MOSFET structure with a lower on-resistance  $(R_{on})$  and a high BV was reported [103]. By introducing a RESURF, the structure can realize very low  $R_{on}$  characteristics. Unlike the Schottky barrier gate used in conventional HEMT devices, MOSFET means that the device can apply a higher gate voltage, which can increase the 2D electron gas concentration and the peak current. Besides, the insulator and AlGaN epitaxial layer can ensure extremely low leakage and allow a large negative to positive gate voltage swing.

In addition to investigations in high-power areas, the RF performances of GaN-based devices have also been studied in recent years due to their potential in MMW field. In 2014, a novel transistor structure, super-lattice castellated FET (SLCFET) based on a GaN super-lattice channel with a 3D gate on SiC substrate was reported [104]. These transistors showed an RF switch figure-of-Merit (FOM) of 2.1 THz, which is 3–10 fold greater than that of the conventional transistors. The  $f_T$  and  $f_{max}$  of SLCFET structure with  $L_g = 0.25 \ \mu m$  are 52 and 53 GHz, respectively. In 2015, GaN HEMTs with ultrathin AlN barrier were presented. By using sub-10 nm AlN barrier, devices with 120 nm gate achieved an  $f_T$  of 75 GHz and an  $f_{max}$  of 202 GHz [105]. In addition to using AlGaN and AlN barriers, InAlGaN is also a very attractive material. A novel InAlGaN/GaN HEMT with  $L_g = 80$  nm was demonstrated in 2015, which also improved the RF performances of devices [106]. In 2016, the devices using N-polar GaN material with 45 nm gate achieved peak  $f_T$  of 160 GHz and  $f_{max}$  of 269 GHz [107].

Except for d-mode GaN based HEMTs, e-mode GaN based NMOS transistors with excellent RF characteristics have also been investigated recently. In 2019, high-K dielectric e-mode GaN based transistors fabricated on an HR Si (111) substrate with  $L_g = 50$  nm were reported. These devices showed excellent RF performance of  $f_T = 190$  GHz and  $f_{\text{max}} = 300$  GHz [108]. By introducing robust gate dielectric and

Figure 11 (Color online) Development of GaN based devices in high-power and high-frequency areas.

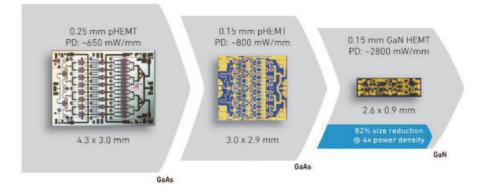

Figure 12 (Color online) Comparison of GaN and GaAs MMIC in size and power density.

epitaxial layers, the RF performance of e-mode GaN based NMOS transistors mentioned above was improved with a record  $f_T$  of 200 GHz and  $f_{\text{max}}$  of 350 GHz in 2020 [109]. Figure 11 shows the development of GaN based devices in high-power and high-frequency areas.

Figure 12 shows the size and power comparison of the monolithic microwave integrated circuit (MMIC). Based on the powerful performance of the GaN-based devices, the related circuit design has a smaller size and stronger performance than GaAs MMIC.

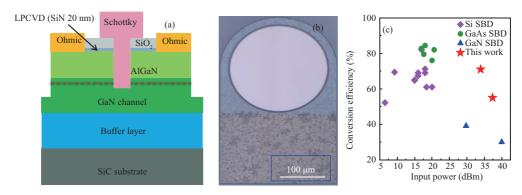

In addition to three-terminal devices such as HEMT, WBG semiconductors are also suitable for the two-terminal Schottky diodes (SBDs) [110,111]. The SBD is suitable for the microwave rectification due to low turn-on voltage ( $V_{\rm on}$ ), while the WBG nature endows the SBD to possess a high BV. For instance, in order to improve the ideality of SBD, a GaN SBD with a hybrid anode and a groove-type low work-function metal structure was proposed [110], which showed several advantages such as ultra-low  $V_{\rm on}$ , high reliability, low leakage, and high consistency. In addition, as shown in Figures 13(a) and (b), a lateral GaN-on-SiC SBD was proposed, which achieved a very low  $V_{\rm on}$  of 0.38 V, an ideality factor of 1.03, a subthreshold swing of 62 mV/dec, and a BV of more than 200 V @IR = 3  $\mu$ A/mm with an electrode spacing of 4  $\mu$ m [110]. A 5.8 GHz high-power microwave rectification circuit was realized based on this SBD. The single-tube microwave rectification power reached 6 W, and the rectification peak efficiency was higher than 70%, as shown in Figure 13(c). The single-tube circuit power is 50–100 times that of Si and GaAs SBDs, which represents the highest international level of microwave high-power SBD and

Figure 13 (Color online) (a) Cross-sectional schematic view of the lateral GaN-on-SiC SBD; (b) microscopy image of the fabricated lateral GaN SBD; (c) conversion efficiency versus input power of some state-of-the-art rectifier circuit with Si, GaAs, and vertical GaN SBDs. The groove-type lateral GaN SBD presents the best combination of  $\eta$ RF/DC and Pin [111] @Copyright 2020 IEEE.

rectifier circuit.

GaN-based SBDs also show a great potential for the next generation power electronics [112–114]. By using lower work-function metal molybdenum (Mo), lateral GaN SBDs demonstrated an ultra-low  $V_{\rm on}$  of 0.31 V, a high BV of 2.46 kV with a high-power FOM of 2.65 GW/cm<sup>2</sup> [113]. The development of anode engineering could further improve device characteristics to BV > 3 kV,  $V_{\rm on}$  of 0.38 V, and a high-power FOM of more than 3 GW/cm<sup>2</sup> [114].

$Al_xGa_{1-x}N$  as ultra-wide bandgap semiconductor is more suitable for high temperature and high voltage applications due to its larger Eg (3.4 to 6.2 eV) [115–118]. Thanks to the improvements of the material growth quality,  $Al_xGa_{1-x}N$ -based electronic devices have also made a lot of progresses in recent years. The 5% Al composition AlGaN channel SBD shows better temperature degradation immunity when compared with GaN channel SBD in both on and off states. The leakage current of the AlGaN channel SBD only increased by 3.5 times from 300 to 425 K, while that of GaN channel SBD increased by 27.8 times [115]. As for high-Al application [116], it is suggested to use 85% AlGaN as an alternative channel material by considering the shallower activation energy of donor in GaN [117], without compromising the breakdown characteristics of AlN. Lateral  $Al_{0.85}Ga_{0.15}N$  SBDs demonstrate a surface root-mean-square roughness of 0.33 nm, a high BV of 2 kV and an ideality factor of 2.3 [118].

Although GaN-based devices have been extensively studied, there are still lots of problems to be solved. In the future, the heat dissipation problem caused by ultra-high power requires special attention. The research on the reliability of the device is still not in-depth enough. Other problems, related to commercialization, such as gold-free ohmic contact research, need more attention as well. Only when such problems are solved can the commercialization of GaN be further promoted to integrate with existing Si-based CMOS processes.

## 2.10 Quantum chip

The silicon-based quantum computing processes quantum information based on quantum chips fabricated by modern silicon semiconductor technologies. On the one hand, it continues the Moore's Law of classical semiconductor chips. When the characteristic size of classical processors decreases to 5 nm or less, the quantum tunneling effect appears. Using the quantum tunneling effect to build more powerful processors has become one of the important topics of information processing. On the other hand, it has many excellent characteristics, such as compatibility with modern semiconductor technology, the characteristic scale of nanometer scale, easy integration with classical measurement and control circuits, and is expected to break through the limitation of the extremely low-temperature working environment. It is considered as one of the most promising systems to realize universal quantum computing.

Silicon-based spin qubits, in a narrow sense, refers to quantum dots defined by constrained voltages applied to gates constructed on silicon metal oxide or Si/SiGe heterojunction. In the condition of the filling of a single electron, by applying a certain magnetic field, electron spin state splitting into spin up and spin down. Using this two-level system coding quantum bit 0 and 1 states, we can build a single spin qubit and further realize silicon quantum computing. In a broad sense, the substrate materials used for the preparation of quantum dots can also be Si nanowires, Ge heterojunction, and other semiconductor materials. The formation of single electron can be obtained utilizing donor doping or single donor injection

| Year      | 2004–2007                                                                        |                                     | 2008                                      | 2009   | 2010      | 2011       | 2012       | 2013        | 2014                 | 2015     | 2016                                                                                         | 2017                   | 2018                            | 2019                  |

|-----------|----------------------------------------------------------------------------------|-------------------------------------|-------------------------------------------|--------|-----------|------------|------------|-------------|----------------------|----------|----------------------------------------------------------------------------------------------|------------------------|---------------------------------|-----------------------|

| UNSW      | Multi-layer SE                                                                   | ΕT                                  | Few electro                               | on QD  | Charge s  | sensing of | QD         |             | Single a<br>qubit ga |          | <ul> <li>ST read</li> <li>EDSR</li> <li>Optimi</li> <li>RB of t</li> <li>Gate set</li> </ul> | zed pulse<br>two qubit |                                 |                       |

|           |                                                                                  | Single shot read of donor Donor que |                                           |        |           | ubit       | High fid   | elity       | Two qub              | oit gate |                                                                                              |                        |                                 |                       |

| TuDelft   | <ul> <li>Single shot re</li> <li>Two spin state</li> <li>Single qubit</li> </ul> |                                     | <ul><li>Nuclear</li><li>Echo</li></ul>    |        | Two qub   | oit gate   | Si/SiG     | e single qu | ıbit                 | Benchm   | arking                                                                                       | Two qu                 | ibit gate                       | RB of<br>two<br>qubit |

|           | control<br>• EDSR                                                                |                                     |                                           |        | Triple qu | uantum do  | ot         |             | Spin shu             | ıttle    | Simulatio                                                                                    | m                      |                                 |                       |

| Princeton |                                                                                  |                                     | <ul><li>EDSR of</li><li>cQED of</li></ul> |        |           |            |            | Maser       |                      |          | Strong<br>coupling                                                                           | Spin pl<br>couplin     |                                 |                       |

|           |                                                                                  |                                     | • Si/SiGe DQD                             |        |           |            |            |             | New Si DQD QD array  |          | Single and two shut qubit gate                                                               |                        | shuttle                         |                       |

| Sandia    |                                                                                  |                                     |                                           | MOS DO | QD        | Donor ir   | nplantatic | 'n          | Cryo-Hl              | EMT      | -                                                                                            | Lat     PS             | qubit<br>tching<br>B<br>t-donor | New<br>MOS<br>QD      |

| HRL       |                                                                                  |                                     |                                           |        | ST qubit  |            | New DQ     | )D          |                      | EOqubi   | t                                                                                            | Benchn                 | narking of                      | `EO qubit             |

| CEA       |                                                                                  |                                     |                                           |        |           | Single Q   | D          | Rf sensi    | ng                   | Hole qu  | bit                                                                                          | Electro                | on qubit                        | rf                    |

Hao Y, et al. Sci China Inf Sci October 2021 Vol. 64 201401:19

**Figure 14** (Color online) Research trends of major research groups in semiconductor quantum computing. SET: single electron transistor. EDSR: electric-dipole spin resonance; QD: quantum dot; cQED: circuit quantum electrodynamics; DQD: double quantum dot; ST: singlet-triplet; HEMT: high electron mobility transistor; RB: randomized benchmarking; PSB: Pauli spin blockade; EO: exchange only.

in Si substrate, besides the use of gate trapped quantum dots. The coding of qubits includes not only the single spin state, but also the two-electron spin singleton-triplet state, the spin-charge hybrid state.

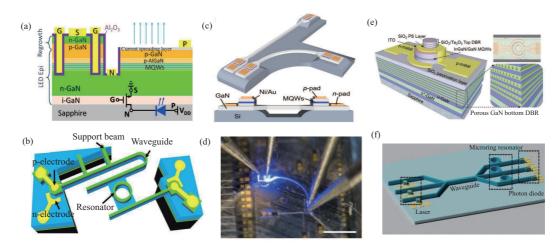

Figure 14 shows the research trends of major international research groups in semiconductor quantum computing (including earlier research on III-V semiconductors). In recent years, a series of important research advances have been made in the fields of spin qubit readout, logic gate control, remote qubit coupling, high-temperature qubit. Since 2014, silicon-spin-based single qubit, two qubits manipulation, three qubits entanglement, single photon-spin strong coupling, fast high-fidelity single spin RF-readout, the millimeter-level resonance of two distant spins and high-temperature spin qubits (> 1 K) have been realized successfully [119,120]. Among these experiments, the fidelity of single-qubit manipulation reached 99.9% [121], the fidelity of two qubits manipulation achieved 98% [122], the fidelity of three qubits entanglement reached 88% [123], the fidelity of spin qubit readout reached 99% [124], and the readout time decreased to 1 millisecond. Especially, the 1 K temperature control of silicon-based qubits not only enables the qubit number to be highly integrated, but also enables the control circuits of the qubits to be integrated with the qubits on the same chip, which provides an extended scheme for the practical quantum processor.