April 2021, Vol. 64 149402:1–149402:2 https://doi.org/10.1007/s11432-019-2846-9

## High mobility germanium-on-insulator p-channel FinFETs

Huan LIU, Genquan  $\mathrm{HAN}^*,$  Jiuren  $\mathrm{ZHOU}^*,$  Yan LIU & Yue HAO

State Key Discipline Laboratory of Wide Band Gap Semiconductor Technology, School of Microelectronics, Xidian University, Xi'an 710071, China

Received 14 October 2019/Revised 4 February 2020/Accepted 18 March 2020/Published online 25 November 2020

Dear editor,

• LETTER •

Over the past decade, germanium has attracted great interest as a promising channel material for p-channel metal oxide semiconductor field-effect-transistor (MOSFET), owing to its higher hole mobility over Si [1]. Tremendous efforts were devoted to solving the technical issues for its practical applications, including source/drain (S/D) ohmic contact formation, strain engineering, channel surface passivation, and gate dielectric engineering [2]. In particular, it is reported that the the effective hole mobility ( $\mu_{\text{eff}}$ ) of Ge pMOSFET can be effectively enhanced by the reduced density of interface trap via gate dielectric engineering [3].

$ZrO_2$ , one of the most promising dielectric materials [4,5], demonstrates both excellent dielectric properties and ferroelectricity, which play a critical role for future CMOS technology in 'More than Moore' era [6]. Studies have shown that a GeO<sub>2</sub> interfacial layer can decompose and intermix with the  $ZrO_2$  layer during thermal annealing, decreasing CET [7]. However, there is still a lack of experimental investigation on Ge p-channel FinFETs with  $ZrO_2$  dielectric.

In this study, Ge p-channel FinFETs with ZrO<sub>2</sub> dielectric are fabricated on (100)-oriented germanium-on-insulator (GeOI), which demonstrates the improved  $\mu_{\rm eff}$  compared to Si universal mobility. The impacts of fin direction on the electrical performance of the devices are also discussed.

Device fabrication. GeOI wafer with 100 nm top Ge(100) film and ~150 nm buried oxide is used for the FinFET fabrication. A phosphorous ion (P<sup>+</sup>) implantation with a dose of  $1 \times 10^{13}$  cm<sup>-2</sup> and an energy of 45 keV is carried out, followed by the thermal annealing at 700°C to form the nwell. And then, S/D regions were defined and implanted using BF<sub>2</sub><sup>+</sup> with a dose of  $1 \times 10^{15}$  cm<sup>-2</sup> and an energy of 30 keV. After that, dry etching is used to reduce the top Ge to about 50 nm. Fins are formed by the patterning using e-beam lithography and dry etching. After a pre-gate cleaning, the wafers are loaded into an atomic layer deposition chamber for the formation of the 4.5 nm ZrO<sub>2</sub> gate dielectric layer at 300°C. Zr[N(CH<sub>3</sub>)<sub>2</sub>]<sub>4</sub> and H<sub>2</sub>O are used as the precursors of Zr and O, respectively. During deposition, the Zr[N(CH<sub>3</sub>)<sub>2</sub>]<sub>4</sub> source is heated to 85°C. Subsequently, a TaN gate layer is deposited. After this layer is patterned to form the gate electrodes, Nickel S/D metal electrodes are then formed by a lift-off process into S/D regions. Finally, thermal annealing at 450°C for 30 s is carried out for the S/D dopant activation and improvement of the gate stack.

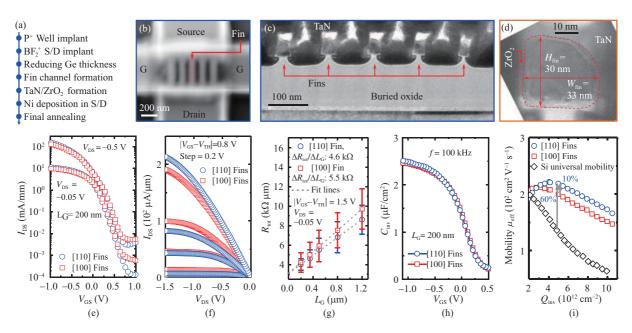

Figure 1(b) shows the top-view scanning electron microscope (SEM) image of the fabricated Ge pFinFET on GeOI. Figure 1(c) shows the transmission electron microscope (TEM) image of pFinFET with several parallel fins. Highresolution TEM (HRTEM) in Figure 1(d) demonstrates that fin with ( $W_{\text{fin}}$ ) and fin height ( $H_{\text{fin}}$ ) are 30 nm and 33 nm, respectively, which is surrounded by the interfacial layer of GeO<sub>x</sub> and the dielectric of ZrO<sub>2</sub>.

Results and discussion. Figure 1(e) shows the measured drain current ( $I_{\rm DS}$ ) vs. gate voltage ( $V_{\rm GS}$ ) curves at different drain voltage ( $V_{\rm DS}$ ) for a pair of GeOI pFinFETs with fin directions of [110] and [100]. Similar subthreshold swing (SS) of 160 mV/decade and ON to OFF current ratio ( $I_{\rm ON}/I_{\rm OFF}$ ) of 5 orders is observed for the two channel directions, indicating the same fin dimension of the devices. SS of the GeOI FinFETs can be reduced by optimizing the surface passivation and decreasing the  $W_{\rm fin}$  of the devices. The  $I_{\rm DS}$ - $V_{\rm DS}$  curves at different gate overdrive | $V_{\rm GS} - V_{\rm TH}$ | in Figure 1(f) show that drive current in device with [110] fin direction is higher than that of the transistor with [100] channel direction. Here,  $V_{\rm TH}$  is defined as  $V_{\rm GS}$  corresponding to  $I_{\rm DS} = 10^{-7}$  A/µm. The boosted  $I_{\rm DS}$  for [110] fin device is attributed to an improved  $\mu_{\rm eff}$ .

Figure 1(g) shows the statistical plots for total on-state resistance ( $R_{\rm tot}$ ) of GeOI pFinFETs with fin directions of [110] and [100], measured at a gate overdrive of 1.5 V and  $V_{\rm DS}$  of -0.05 V. S/D resistance ( $R_{\rm SD}$ ) and channel resistivity  $\Delta R_{\rm tot}/\Delta L_{\rm G}$  are extracted from the y-intercept and slope of this plot, respectively. The same RSD of  $\sim 3 \ k\Omega\mu m$  is obtained for the devices with different channel directions.  $\Delta R_{\rm tot}/\Delta L_{\rm G}$  related to the inversion charge density ( $Q_{\rm inv}$ ) and  $\mu_{\rm eff}$  are extracted to be 4.6 and 5.5 k $\Omega$  for [110] and [100] FinFETs, respectively.  $Q_{\rm inv}$  is calculated from the inversion capacitance ( $C_{\rm inv}$ ) vs.  $V_{\rm GS}$  curves in Figure 1(h). GeOI FinFETs have a capacitance equivalent thickness (CET) value

<sup>\*</sup> Corresponding author (email: zhoujiuren@163.com, gqhan@xidian.edu.cn)

Figure 1 (Color online) (a) Key process steps for fabricating GeOI FinFETs; (b) SEM and (c) TEM images of GeOI FinFETs with parallel fins; (d) HRTEM showing a Ge fin with  $W_{\rm fin}$  of ~33 nm and Hfin of ~30 nm; (e) measured  $I_{\rm DS}$ - $V_{\rm GS}$  curves of a pair of GeOI FinFETs with fin directions of [110] and [100]; (f)  $I_{\rm DS}$ - $V_{\rm DS}$  curves showing that device with fin direction of [110] has a higher  $I_{\rm DS}$  compared to the transistor along [100]; (g)  $R_{\rm tot}$  vs.  $L_{\rm G}$  for GeOI FinFETs measured at  $|V_{\rm GS} - V_{\rm TH}| = 1.5$  V and  $V_{\rm DS} = -0.05$  V; (h)  $C_{\rm inv}$ - $V_{\rm GS}$  characteristics measured at a frequency of 100 kHz for the GeOI FinFETs; (i)  $\mu_{\rm eff}$  vs.  $Q_{\rm inv}$ , extracted using the split C-V method. Higher  $\mu_{\rm eff}$  is achieved in GeOI FinFETs compared to Si universal mobility.

of 1.5 nm, owing to the high  $\kappa$  value of 23~25 of ZrO\_2 dielectric [4].

$\mu_{\rm eff}$  as a function of  $Q_{\rm inv}$  curves calculated as  $1/[WQ_{\rm inv}(\Delta R_{\rm tot}/\Delta L_{\rm G})]$  is shown in Figure 1(i), which demonstrates that GeOI FinFETs have a significantly improved  $\mu_{\rm eff}$  compared to Si universal mobility. GeOI FinFETs with channel direction of [110] have a 10% improved  $\mu_{\rm eff}$  at a Qinv of  $5\times10^{12}~{\rm cm}^{-2}$  in comparison with transistors along [100] direction. It was experimentally demonstrated that (110)-oriented Ge p-channel transistors have a higher hole mobility than that of the devices on (100) surface [8,9]. Furthermore, it was found that [110] fins have a better sidewall surface roughness compared to the [100] fins during the device fabrication, which might lead to an even higher  $\mu_{\rm eff}$  in [110] GeOI transistors.

Conclusion. We fabricated and investigated the electrical characteristics of Ge pFinFET on (100)-oriented GeOI wafer. Transistors with fin channel along [110] direction demonstrate the improved drive current and channel  $\Delta R_{\rm tot}/\Delta L_{\rm G}$  compared to the devices along [100] direction. At a  $Q_{\rm inv}$  of  $5 \times 10^{12}$  cm<sup>-2</sup>, GeOI FinFETs along [110] direction have 60% and 10% improved  $\mu_{\rm eff}$  in comparison with [100] devices and Si university mobility, respectively.

Acknowledgements This work was supported by National Key Research and Development Project (Grant Nos. 2018YFB2200500, 2018YFB2202800) and National Natural Science Foundation of China (Grant Nos. 61534004, 61604112, 61622405, 61874081, 61851406).

## References

1 Liu B, Gong X, Zhan C, et al. Germanium multiple-gate field-effect transistors formed on germanium-on-insulator substrate. IEEE Trans Electron Dev, 2013, 60: 1852–1860

- 2~Gong X, Han G, Bai F, et al. Germanium-Tin (GeSn) p-Channel MOSFETs fabricated on (100) and (111) surface orientations with sub-400°C Si\_2H\_6 passivation. IEEE Electron Dev Lett, 2013, 34: 339–341

- 3 Zhang R, Taoka N, Huang P-C, et al. 1-nm-thick EOT high mobility Ge n- and p-MOSFETs with ultrathin  ${\rm GeO}_x/{\rm Ge}$  MOS interfaces fabricated by plasma post oxidation. In: Proceedings of International Electron Devices Meeting, Washington, 2011. 642–645

- 4 Liu H, Han G, Xu Y, et al. Germanium-Tin (GeSn) pchannel MOSFETs fabricated on (100) and (111) surface orientations with sub-400°C Si<sub>2</sub>H<sub>6</sub> passivation. IEEE Electron Dev Lett, 2019, 40: 371–374

- 5 Lin C-M, Chang H-C, Chen Y-T, et al. Interfacial layer-free ZrO<sub>2</sub> on Ge with 0.39-nm EOT,  $\kappa \sim 43$ ,  $\sim 2 \times 10^{-3}$  A/cm<sup>2</sup> gate leakage, SS =85 mV/dec,  $I_{\rm on}/I_{\rm off} = 6 \times 10^5$ , and high strain response. In: Proceedings of International Electron Devices Meeting, San Francisco, 2012. 1–4

- 6 Müller J, Böscke T S, Schröder U, et al. Ferroelectricity in simple binary ZrO<sub>2</sub> and HfO<sub>2</sub>. Nano Lett, 2012, 12: 4318-4323

- 7 Kamata Y, Kamimuta Y, Ino T, et al. Influences of activation annealing on characteristics of Ge p-MOSFET with ZrO<sub>2</sub> gate dielectric. In: Proceedings of International Conference on Solid State Devices and Materials, 2005. 856–857

- 8 Dissanayake S, Tomiyama K, Sugahara S, et al. High performance ultrathin (110)-oriented ge-on-insulator pchannel metal-oxide-semiconductor field-effect transistors fabricated by Ge condensation technique. Appl Phys Express, 2010, 3: 041302

- 9 Wong I H, Chen Y T, Yan J Y, et al. Fabrication and low temperature characterization of Ge (110) and (100) p-MOSFETs. IEEE Trans Electron Dev, 2014, 61: 2215–2219