# SCIENCE CHINA Information Sciences

• RESEARCH PAPER •

February 2020, Vol. 63 122401:1–122401:7 https://doi.org/10.1007/s11432-019-9836-9

# Vertical $SnS_2/Si$ heterostructure for tunnel diodes

# Rundong JIA, Qianqian HUANG<sup>\*</sup> & Ru HUANG<sup>\*</sup>

Key Laboratory of Microelectronic Devices and Circuits (MOE), Institute of Microelectronics, Peking University, Beijing 100871, China

Received 23 January 2019/Accepted 15 March 2019/Published online 16 September 2019

Abstract Tunneling FET (TFET) is considered as one of the most promising low-power electronic devices, however, suffers from the low drive current. Heterostructure TFET with low effective tunnel barrier height based on traditional 3D materials can obtain large tunnel current but deteriorated off-state current induced by the lattice mismatch. van der Waals heterostructure TFET based on 2D materials can obtain dangling-bond-free interface for suppressed off-state current but face the challenge of controllable and stable doping technology. As the critical building block of the TFET, tunnel diode based on the 2D/3D heterostructure is proposed in this study and experimentally demonstrated. Combination of the pristine interface of 2D materials and matured doping technology in the traditional 3D bulk materials, tunnel diodes based on the 2D/3D heterostructures are expected to realize low leakage current and high on current simultaneously, showing great potential in low-power electronics. The N<sup>+</sup> SnS<sub>2</sub>/P<sup>+</sup> Si heterostructure with effective tunnel barrier of 0.17 eV theoretically is considered for the first time and selected as the optimal material platform for tunnel diodes. The N<sup>+</sup> SnS<sub>2</sub>/P<sup>+</sup> Si tunnel diode demonstrated experimentally shows the high current density of 1  $\mu$ A/ $\mu$ m<sup>2</sup>, which is the highest one among the reported tunnel diodes based on the 2D/group IV materials. The tunneling current is also confirmed by low-temperature measurements. This study shows the great potential of the 2D/3D heterostructure for low-power tunneling devices.

Keywords 2D/3D heterostructure, SnS<sub>2</sub>/Si, tunnel barrier, tunnel diode, energy-efficient

#### 1 Introduction

For conventional metal-oxide-semiconductor field-effect transistor (MOSFET), power consumption has become the biggest bottleneck for further scaling down. The key obstacle is from the fundamental thermionic limitation of the subthreshold slope (SS) in MOSFET [1,2]. Tunneling FET (TFET), which can break the above limit and possess the subthermionic subthreshold slope due to its band-to-band tunneling (BTBT) mechanism, has become one of the most promising candidates for future low-power applications, especially for low standby-power application [1,2]. However, the tunneling current is relatively low for silicon-based TFETs due to the relatively large tunnel barrier height. Heterostructure TFETs based on traditional bulk materials, such as SiGe, InAs, GaAs, have been widely investigated due to the relatively low effective tunnel barrier height for high tunneling efficiency and high tunneling current [3,4]. However, the lattice mismatch at the heterostructure interface will introduce interface states which may cause the trap-assisted tunneling current and deteriorate the off-state current and on/off current ratio [4]. Recently, TFETs based on van der Waals heterostructures composed of two-dimensional (2D) materials have gained tremendous research interest due to their dangling-bond-free interfaces [5–11].

<sup>\*</sup> Corresponding author (email: hqq@pku.edu.cn, ruhuang@pku.edu.cn)

The dangling-bond-free interface could mitigate the parasitic trap-assisted tunneling induced by interface states. However, for 2D TFETs, the doping technology in 2D materials is very challenging and the controllable and stable doping is difficult to obtain for the source or drain [5]. Since the doping technology in traditional 3D bulk materials is highly matured compared with that in 2D materials [5], the heterostructure TFET combining a 2D material as the channel and a 3D bulk material as the source is supposed to obtain highly doped source and pristine interface of the heterostructure simultaneously [2]. The 2D material as the channel will enhance the gate controllability for steeper subthreshold slope. The interface between the 2D material and 3D material is still van der Waals interacted without lattice matching for low off-state current [2, 6]. The presence of the van der Waals gap at the interface also enables the ultra-sharp doping profile of the source tunnel junction for high tunneling field and thus high tunneling current [2, 12]. Moreover, the contact resistance of the 3D materials to metal can also be reduced compared with that of the 2D materials to metal [13]. Consequently, TFETs based on the 2D/3D heterostructures are expected to realize low leakage current and high on current simultaneously, and show the great potential in low-power electronics. Tunnel diode based on the 2D/3D heterostructures is the critical building block of the above TFET. However, only a few experimental studies have been reported regarding the tunnel diodes or devices based on the 2D/3D heterostructures. P<sup>+</sup> MoS<sub>2</sub>/N<sup>+</sup> GaN, N<sup>+</sup>  $MoS_2/P^+$  Ge and N<sup>+</sup>  $MoS_2/P^+$  Si tunnel diodes have been reported [2, 12, 14]. However, the band alignment of these 2D/3D heterostructures is either type I ( $P^+$  MoS<sub>2</sub>/ $N^+$  GaN) or type II with relatively high effective tunnel barrier height (0.4 eV in N<sup>+</sup>  $MoS_2/P^+$  Ge and 0.78 eV in N<sup>+</sup>  $MoS_2/P^+$ Si), leading to the limited tunneling current densities. Therefore, performance improvement of 2D/3Dtunnel diodes or devices with high current density are still in urgent need.

In this study, the N<sup>+</sup> SnS<sub>2</sub>/P<sup>+</sup> Si heterostructure with effective tunnel barrier height of 0.17 eV theoretically is considered for the first time and selected as the optimal material platform for tunnel diode. The fabricated N<sup>+</sup> SnS<sub>2</sub>/P<sup>+</sup> Si tunnel diode shows the current density of 1  $\mu$ A/ $\mu$ m<sup>2</sup>, which is the highest one among the reported tunnel diodes based on the 2D/group IV materials. The tunneling current is also confirmed by low-temperature measurements. This study shows the great potential of the 2D/3D heterostructure for low-power tunneling devices.

### 2 Device physics and fabrication

#### 2.1 Device physics

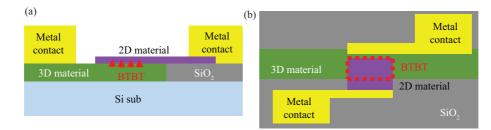

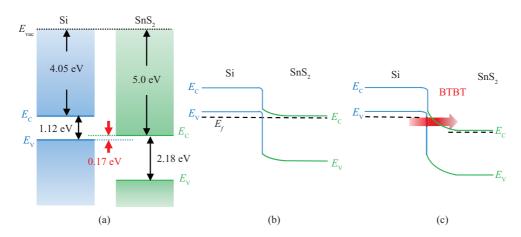

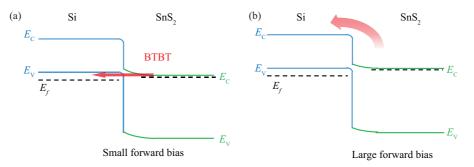

Figure 1 shows the schematic structure and top view of the vertical 2D/3D tunnel diode in this study. The 3D material is highly doped and the 2D material is designed to be the opposite type to form the P/N heterojunction. The 2D material sheet is designed above the 3D material for the future transistor fabrication. Considering that most of the 2D materials show n-type characteristics due to the structural defects [15], the doping of 3D material is designed to be p-type in this study. The band alignment of the 2D/3D heterostructure is designed to be type-II, in which the conduction band of the n-type 2D material layer is above the valence band of the p-type 3D material. The heterostructure of type-II band alignment with low effective tunnel barrier height enables the high tunneling efficiency and thus the high tunneling current. According to the band structures of various 2D semiconductors and 3D bulk materials, since the electronic affinity of  $SnS_2$  is relatively large compared to other 2D semiconductors and relatively low effective tunnel barrier height can be formed for the  $SnS_2/Si$  heterostructure, N<sup>+</sup>  $SnS_2/P^+$  Si heterostructure stands out as the superior material platform for tunnel diode. Figure 2 illustrates the operation mechanism of the vertical  $N^+$   $SnS_2/P^+$  Si tunnel diode. Figure 2(a) illustrates the bandgaps and electronic affinities of Si and  $SnS_2$ , and the tunnel barrier height is determined to be 0.17 eV theoretically [16]. Figure 2(b) illustrates the band diagram of the N<sup>+</sup>  $SnS_2/P^+$  Si tunnel diode in the equilibrium state. Electrons in the valence band of the p-type Si cannot tunnel into the conduction band of the n-type  $SnS_2$  layer since there is no tunneling window. When the negative voltage is applied to the Si contact, the tunnel diode is biased in the reverse region. The conduction band energy  $(E_{\rm C})$  of the n-type  $SnS_2$  begins to be lower than the valence band energy  $(E_V)$  of the p-type Si, and the tunneling

**Figure 1** (Color online) (a) Schematic view of the vertical 2D/3D tunnel diode. Vertical tunneling occurs across the overlap region between the 2D material and the 3D material. (b) Top view of the vertical 2D/3D tunnel diode.

Figure 2 (Color online) The band diagram of the  $N^+ SnS_2/P^+$  Si tunnel diode. (a) The bandgaps and electronic affinities of Si and SnS<sub>2</sub>; (b) the equilibrium state; (c) the working state-reverse bias region.

current across the  $SnS_2/Si$  heterostructure dominates and increases accordingly.

#### 2.2 Device fabrication

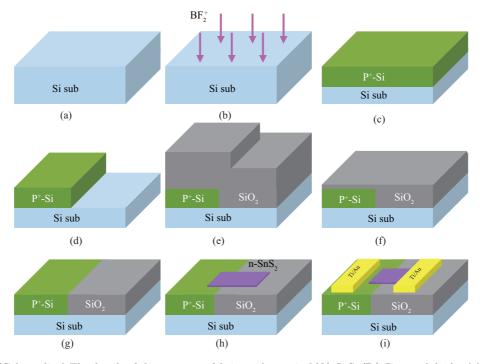

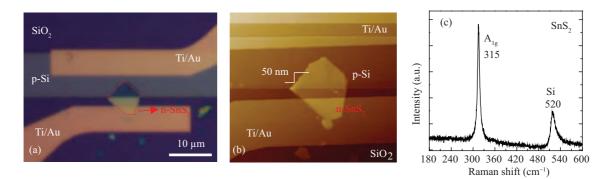

The details of the process used to fabricate the vertical  $\text{SnS}_2/\text{Si}$  tunnel diode are illustrated in Figure 3. The lightly-doped Si(100) substrate is firstly prepared, and the impurity  $\text{BF}_2^+$  is implanted successively with doping density of  $1 \times 10^{21}$  cm<sup>-3</sup>. After lithography, Si is selectively dry-etched to form trenches. Then SiO<sub>2</sub> is formed by chemical vapor deposition (CVD) and is treated by chemical mechanical polishing (CMP) to flatten the surface. The wafer is then treated in hydrofluoric acid (HF) in order to remove the residual SiO<sub>2</sub> and the native oxide on the Si surface. Then the SnS<sub>2</sub> sheet is mechanically exfoliated onto the Si substrate within a short time interval to minimum the growth of native oxide and thus the 2D/3D heterostructure is formed. Metal contacts were sequentially defined by electron beam lithography, electron beam evaporation and lift-off process. In order to reduce the contact resistance of metal-SnS<sub>2</sub> for better device performance, Ti ( $W_m = 4.33 \text{ eV}$ ) was adopted for realizing n-type contacts and the low Schottky barrier for electrons at the SnS<sub>2</sub>/Ti interface due to its low working function. Figure 4(a) shows the optical image of a fabricated SnS<sub>2</sub>/Si vertical tunnel diode in this study. The thickness SnS<sub>2</sub> in this tunnel diode is about 50 nm, measured by the atomic force microscope (AFM), as shown in Figure 4(b). The characteristic Raman peaks of SnS<sub>2</sub> can be distinctly observed, as shown in Figure 4(c). The A<sub>1</sub>g peak of SnS<sub>2</sub> is observed at 315.0 cm<sup>-3</sup>.

## 3 Results and discussion

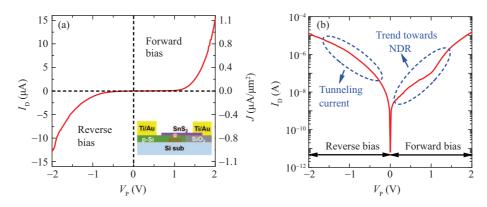

Figure 5 shows the measured electrical characteristics of the N<sup>+</sup>  $SnS_2/P^+$  Si tunnel diode at room temperature. The results are obtained by applying the bias  $V_P$  on Si contact, with  $SnS_2$  contact grounded. Figure 5(a) shows the bidirectional conductivity. The thermionic emission current dominates in the forward bias region, while the Zenner tunneling current dominates in the reverse bias region. The N<sup>+</sup>

Jia R D, et al. Sci China Inf Sci February 2020 Vol. 63 122401:4

Figure 3 (Color online) The details of the process to fabricate the vertical  $N^+ SnS_2/P^+$  Si tunnel diode. (a) The original Si substrate; (b) ion implantation with  $BF_2^+$ ; (c) highly p-doped Si; (d) dry etching to form trenches; (e) CVD of SiO<sub>2</sub>; (f) CMP of SiO<sub>2</sub>; (g) HF treatment to remove the residual and native oxide; (h) transfer of SnS<sub>2</sub> sheet; (i) formation of contacts.

Figure 4 (Color online) (a) The optical microscope image of the fabricated vertical  $N^+ SnS_2/P^+$  Si tunnel diode; (b) AFM image of fabricated vertical  $N^+ SnS_2/P^+$  Si tunnel diode; (c) Raman characterization of the SnS<sub>2</sub> sheet in the tunnel diode.

$SnS_2/P^+$  Si tunnel diode exhibits high Zenner tunneling current of 12.8 µA and the tunneling current density is 1 µA/µm<sup>2</sup>, which is higher than that in the reported N<sup>+</sup> MoS<sub>2</sub>/P<sup>+</sup> Ge and N<sup>+</sup> MoS<sub>2</sub>/P<sup>+</sup> Si tunnel diodes [2,12], further confirming the optimized band alignment of the N<sup>+</sup> SnS<sub>2</sub>/P<sup>+</sup> Si heterostructure. In the N<sup>+</sup> MoS<sub>2</sub>/P<sup>+</sup> Ge tunnel diode, the relatively larger effective tunnel barrier height (0.4 eV), together with the native oxide of Ge at the interface which is formed during the fabrication process, limits the current density of the tunneling devices [2]. In the N<sup>+</sup> MoS<sub>2</sub>/P<sup>+</sup> Si tunnel diode, although the band diagram changes from type-I to type-II as the thickness of MoS<sub>2</sub> increases from the monolayer to the bulk, the tunnel diode exhibits the unsatisfactory tunneling current due to the large effective tunnel barrier height (0.78 eV) [14]. However, in the N<sup>+</sup> SnS<sub>2</sub>/P<sup>+</sup> Si tunnel diode of this study, the effective tunnel barrier height is optimized to be 0.17 eV which is much lower than that in the N<sup>+</sup> MoS<sub>2</sub>/P<sup>+</sup> Ge or N<sup>+</sup> MoS<sub>2</sub>/P<sup>+</sup> Si tunnel diodes. According to the results in [12, 17–19], SnS<sub>2</sub> with thickness of 50 nm is partially depleted. Although the thickness of SnS<sub>2</sub> in this experiment is relatively large, the tunneling current density is still the highest one compared with that of N<sup>+</sup> MoS<sub>2</sub>/P<sup>+</sup> Ge and N<sup>+</sup> MoS<sub>2</sub>/P<sup>+</sup> Si

Figure 5 (Color online) The electric characteristics of the vertical  $N^+ SnS_2/P^+$  Si tunnel diode. (a) Linear and (b) log current-voltage characteristics.

Figure 6 (Color online) The NDR characteristic of the vertical  $N^+ SnS_2/P^+$  Si tunnel diode. (a) The band diagram in the small forward bias region; (b) the band diagram in the large forward bias region.

tunnel diodes. By future decreasing the thickness of  $SnS_2$ , the effective tunneling barrier width can be further reduced and the tunneling current will increase considerably. Furthermore, during the fabrication process, the HF treatment of the silicon substrate removes the native oxide, and thus effectively improves the tunneling efficiency and tunneling current.

As shown in Figure 5(b), a trend towards negative differential resistance (NDR) in the forward bias region is observed and confirms that a heavily-doped N<sup>+</sup> SnS<sub>2</sub>/P<sup>+</sup> Si junction is formed at the interface. To illustrate this phenomenon, the band alignment of the N<sup>+</sup> SnS<sub>2</sub>/P<sup>+</sup> Si tunnel diode under different forward bias conditions is given in Figure 6. In the equilibrium state, the Fermi level in p-type Si and n-type SnS<sub>2</sub> is aligned, as shown in Figure 2(b). As the forward bias  $V_P$  increases, the energy band of Si is pulled down, and a finite tunneling window is created for electrons in the conduction band of SnS<sub>2</sub> to tunnel into the empty states in the valence band of Si. The tunneling current reaches its peak when the Fermi level of SnS<sub>2</sub> aligns with the valence band maximum of Si, as shown in Figure 6. As the increase of the forward bias  $V_P$ , the tunneling window is gradually switched off, meanwhile, the thermionic current begins to dominate and is larger than the tunneling current, leading to the transition from tunneling to thermionic emission and showing a trend towards NDR.

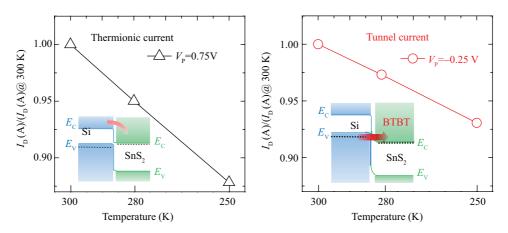

In order to further verify the tunneling mechanism of this vertical  $N^+ SnS_2/P^+$  Si tunnel diode, the dependence of electric characteristics on temperature is studied. Temperature dependence of thermionic current in forward bias and tunneling current in reverse bias region are compared in Figure 7. Both mechanisms of current show positive dependence on temperature. With the decreased temperature, the bandgaps of silicon and  $SnS_2$  relatively increase, which has been experimentally observed in [20,21]. The increased bandgaps will lead to the decreased tunneling probability and decreased current for tunnel diode. For thermionic emission current, the fermi distribution also changes with temperature, and the number of electrons with high energy decreases at low temperature, resulting in the lower thermionic emission current. However, the correlation coefficients of these two kinds of current are different. Tunneling current shows the weaker dependence on temperature than the temperature dependence of the thermionic

Figure 7 (Color online) The temperature characteristic of the vertical  $N^+$   $SnS_2/P^+$  Si tunnel diode.

emission current in the forward bias region, which is the typical feature of tunneling current [22]. This is due to the different sensitivity of the bandgap and the Fermi distribution. Since the bandgap shows the weaker dependence than the Fermi distribution on the temperature, the tunneling current shows the weaker dependence as shown in Figure 7.

#### 4 Conclusion

In conclusion, the N<sup>+</sup> SnS<sub>2</sub>/P<sup>+</sup> Si heterostructure with effective tunnel barrier height of 0.17 eV theoretically is considered for the first time and the vertical tunnel diode is experimentally demonstrated to verify the superiority of the N<sup>+</sup> SnS<sub>2</sub>/P<sup>+</sup> Si heterostructure. This fabricated N<sup>+</sup> SnS<sub>2</sub>/P<sup>+</sup> Si tunnel diode shows the high current density of 1  $\mu$ A/ $\mu$ m<sup>2</sup>, which is the highest one among the reported tunnel diodes based on the 2D/group IV materials. The tunneling current is also confirmed by the low-temperature measurements. This study shows the great potential of the 2D/3D heterostructure for low-power tunneling devices.

Acknowledgements This work was partly supported by National Natural Science Foundation of China (Grant Nos. 61421005, 61851401, 61822401, 61604006) and the 111 Project (Grant No. B18001).

#### References

- 1 Ionescu A M, Riel H. Tunnel field-effect transistors as energy-efficient electronic switches. Nature, 2011, 479: 329-337

- 2 Sarkar D, Xie X, Liu W, et al. A subthermionic tunnel field-effect transistor with an atomically thin channel. Nature, 2015, 526: 91–95

- 3 Zhao Y, Wu C L, Huang Q Q, et al. A novel tunnel FET design through adaptive bandgap engineering with constant sub-threshold slope over 5 decades of current and high  $I_{ON}/I_{OFF}$  ratio. IEEE Electron Device Lett, 2017, 38: 540–543

- 4 Dey A W, Borg B M, Ganjipour B, et al. High-current GaSb/InAs(Sb) nanowire tunnel field-effect transistors. IEEE Electron Device Lett, 2013, 34: 211–213

- 5 Liu Y, Weiss N O, Duan X D, et al. Van der Waals heterostructures and devices. Nat Rev Mater, 2016, 1: 16042

- 6 Roy T, Tosun M, Cao X, et al. Dual-gated MoS2/WSe2 van der Waals tunnel diodes and transistors. ACS Nano, 2015, 9: 2071–2079

- 7 Roy T, Tosun M, Hettick M, et al. 2D-2D tunneling field-effect transistors using WSe<sub>2</sub>/SnSe<sub>2</sub> heterostructures. Appl Phys Lett, 2016, 108: 083111

- 8 Xu J, Jia J Y, Lai S, et al. Tunneling field effect transistor integrated with black phosphorus-MoS<sub>2</sub> junction and ion gel dielectric. Appl Phys Lett, 2017, 110: 033103

- 9 Yan X, Liu C S, Li C, et al. Tunable SnSe<sub>2</sub>/WSe<sub>2</sub> heterostructure tunneling field effect transistor. Small, 2017, 1701478

- 10 Li X F, Gao T T, Wu Y Q. Development of two-dimensional materials for electronic applications. Sci China Inf Sci, 2016, 59: 061405

- 11 Xie Q, Chen C, Liu M J, et al. Short-channel effects on the static noise margin of 6T SRAM composed of 2D semiconductor MOSFETs. Sci China Inf Sci, 2019, 62: 062404

- 12 Krishnamoorthy S, Lee Ii E W, Lee C H, et al. High current density 2D/3D MoS<sub>2</sub>/GaN Esaki tunnel diodes. Appl Phys Lett, 2016, 109: 183505

Jia R D, et al. Sci China Inf Sci February 2020 Vol. 63 122401:7

- 13 Zhang B X, An X, Liu P Q, et al. Improvement of thermal stability of nickel germanide using nitrogen plasma pretreatment for germanium-based technology. Sci China Inf Sci, 2018, 61: 109401

- 14 Xu K, Cai Y H, Zhu W J. Esaki diodes based on 2-D/3-D heterojunctions. IEEE Trans Electron Devices, 2018, 65: 4155–4159

- 15 McDonnell S, Addou R, Buie C, et al. Defect-dominated doping and contact resistance in MoS2. ACS Nano, 2014, 8: 2880–2888

- 16 Schlaf R, Lang O, Pettenkofer C, et al. Band lineup of layered semiconductor heterointerfaces prepared by van der Waals epitaxy: charge transfer correction term for the electron affinity rule. J Appl Phys, 1999, 85: 2732–2753

- 17 Fang N, Nagashio K. Accumulation-mode two-dimensional field-effect transistor: operation mechanism and thickness scaling rule. ACS Appl Mater Interfaces, 2018, 10: 32355–32364

- 18 Jin Y, Keum D H, An S J, et al. A van der Waals homojunction: ideal p-n diode behavior in MoSe2. Adv Mater, 2015, 27: 5534–5540

- 19 Doan M H, Jin Y, Adhikari S, et al. Charge transport in  $MoS_2/WSe_2$  van der Waals heterostructure with tunable inversion layer. ACS Nano, 2017, 11: 3832–3840

- 20 Bludau W, Onton A, Heinke W. Temperature dependence of the band gap of silicon. J Appl Phys, 1974, 45: 1846–1848

21 Burton L A, Whittles T J, Hesp D, et al. Electronic and optical properties of single crystal SnS<sub>2</sub>: an earth-abundant disulfide photocatalyst. J Mater Chem A, 2016, 4: 1312–1318

- 22 Huang Q Q, Huang R, Zhan Z, et al. A novel Si Tunnel FET with 36 mV/dec subthreshold slope based on junction depleted-modulation through striped gate configuration. In: Proceedings of IEEE International Electron Devices Meeting (IEDM), San Francisco, 2012. 187–190