• LETTER •

January 2017, Vol. 60 019102:1–019102:3 doi: 10.1007/s11432-015-0850-4

## MLXR: multi-layer obstacle-avoiding X-architecture Steiner tree construction for VLSI routing

Xing HUANG<sup>1</sup>, Wenzhong GUO<sup>1,2\*</sup>, Genggeng LIU<sup>1</sup> & Guolong CHEN<sup>1,2</sup>

<sup>1</sup>College of Mathematics and Computer Sciences, Fuzhou University, Fuzhou 350116, China; <sup>2</sup>Key Laboratory of Network Computing and Intelligent Information Processing (Fujian Province), Fuzhou University, Fuzhou 350116, China

Received October 26, 2015; accepted December 29, 2015; published online May 16, 2016

Citation Huang X, Guo W Z, Liu G G, et al. MLXR: multi-layer obstacle-avoiding X-architecture Steiner tree construction for VLSI routing. Sci China Inf Sci, 2017, 60(1): 019102, doi: 10.1007/s11432-015-0850-4

## Dear editor,

Rectilinear Steiner minimal tree (RSMT) has been widely used in several modern very large scale integration (VLSI) circuit design phases. Because of its importance, it has been fully studied in the past decades. In addition, the density of modern VLSI chips has increased significantly. In today's VLSI designs, there are increasingly more obstacles, such as IP blocks and pre-routed nets, these obstacles cannot be run through during the routing process, and thus the obstacle-avoiding RSMT (OARSMT) construction problem has received increasing attention in recent years.

On the other hand, with the advance of the manufacturing process, modern VLSI chips can offer several mental layers in order to increase routing flexibility. Therefore, Lin et al. [1] first formulated the multi-layer OARSMT (ML-OARSMT) construction problem. Recently, Liu et al. [2] further proved that the multi-layer model is very different from its single-layer counterpart because the single-layer size is linear, whereas that of the multilayer is  $\Omega(n^2)$ .

As integrated circuits are scaled into very deep submicrometer dimensions, the rectilinear architecture that restricts routing directions to be only horizontal and vertical has not met current design requirements. Fortunately, the emerging X-

\* Corresponding author (email: fzugwz@163.com)

The authors declare that they have no conflict of interest.

architecture, which allows  $45^{\circ}$  and  $135^{\circ}$  routing directions and can further improve routability, has become a popular research topic [3,4].

The problem is that when we simultaneously consider multi-layer, obstacles, and Xarchitecture, namely the multi-layer obstacleavoiding X-architecture Steiner minimal tree (ML-OAXSMT) construction, the design will become more complex. To our best knowledge, there are only a few studies for ML-OAXSMT construction thus far [5–7]. Considering the shortages of the current work and requirements of VLSI design, we develop a new heuristic algorithm for ML-OAXSMT construction in this letter. The main contributions can be summarized as follows. (1) From the overall perspective, we employ a lookup table-based framework for the multi-layer routing problem. The framework is effective for both obstacle-free and obstacle-avoiding cases. (2)Based on fast table lookup, an efficient and effective projection based obstacle-avoiding strategy is proposed, which can accurately capture the appropriate (pseudo) Steiner point locations in multilayer environments, and thus generate a multilayer obstacle-avoiding X-architecture Steiner tree (ML-OAXST). (3) Both the wirelength and runtime of the proposed algorithm are inspiring when compared with previous multi-layer

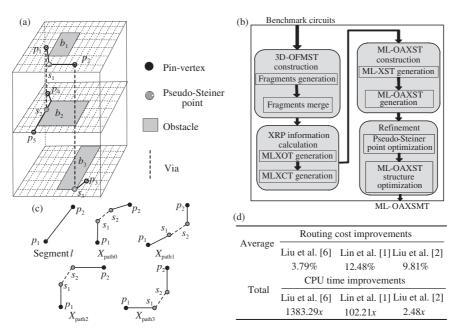

Figure 1 Illustration of algorithm and experimental results. (a) Problem model; (b) algorithm flow chart; (c) four types of X-routing paths; (d) final experimental results with ten benchmark circuits.

obstacle-avoiding algorithms.

**The ML-OAXSMT problem:** Given via cost  $C_v$ , set of n pin vertices P, set of m obstacles B, and  $N_l$  routing layers, we construct multi-layer X-architecture Steiner tree T in order to connect all the pin vertices in P such that no tree edge or via intersects with an obstacle in B, and the total cost of the tree is minimized, where the total cost of the tree is defined as the total wirelength  $+ C_v \times$  the number of vias.

Figure 1(a) shows an example of a three-layer obstacle-avoiding model, there are five pin vertices and three obstacles. One solution with two vias of ML-OAXSMT is also given in Figure 1(a).

**Definition 1** (pseudo-Steiner). For convenience, we assume that the endpoints, with the exception of the pin vertices, are collectively referred to as pseudo-Steiner points.

**Definition 2** (X-routing path). As shown in Figure 1(c), let  $p_1 = (x_1, y_1, z_1)$  and  $p_2 = (x_2, y_2, z_2)$  be the two endpoints of line segment l, where  $x_1 < x_2$ . We define four types of X-routing paths (XRP) between two points in the layers. The  $X_{\text{path0}}$  that corresponds to edge l first leads the rectilinear side from  $p_1$  to pseudo-Steiner point  $s_1$ , it then connects to pseudo-Steiner point  $s_2$  in the other layer by generating a via, and finally leads the non-rectilinear side from  $s_2$  to  $p_2$ .  $X_{\text{path1}}$ ,  $X_{\text{path2}}$  and  $X_{\text{path3}}$  can be defined similarly.

In the following parts, we use  $p_i p_j k$  to represent an XRP between point  $p_i$  and  $p_j$  when using  $X_{\text{path}k}$ .

Algorithm overview. We propose MLXR, which

consists of the four steps outlined below, Figure 1(b) shows the flow of the algorithm.

**Step 1.** A 3D obstacle-free minimal spanning tree (3D-OFMST) is constructed in order to connect all pin vertices in P.

**Step 2.** The XRP information of all 3D-OFMST edges is calculated and recorded into two lookup tables. These two tables can provide information support for the subsequent steps, and thus improve the efficiency of MLXR.

**Step 3.** Based on the information provided by the two lookup tables, a multi-layer X-architecture Steiner tree (ML-XST) is constructed by transforming each 3D-OFMST edge into an XRP. Then, we employ an effective projection based technique to convert ML-XST into ML-OAXST.

**Step 4.** Two refinement strategies are used to further reduce the wire-length of generated ML-OAXST, and thus generate the final ML-OAXSMT.

Independently of single-layer or multi-layer circumstances, MST is widely used to approximate SMT in the VLSI routing problem [4, 6], because MSTs can be constructed easily and converted into SMTs. Therefore, we first construct a 3D-OFMST as the basic skeleton of the final ML-OAXSMT. Because the algorithm proposed by Bentley and Friedman is very mature technology for MST construction in 3D environment [8], we directly employ it in Step 1 in order to construct a 3D-OFMST. In Step 2, given that the 3D-OFMST contains n - 1 edges, and each edge has four different XRP choices, there are  $4 \times (n - 1)$  XRPs in total. Two lookup tables are generated for all XRPs. The first is called the multi-layer XRPobstacle table (MLXOT), which records the relevant information of those obstacles through which each XRP runs. Moreover, considering that each XRP  $p_i p_j k$  has three sub-paths ( $p_i s_{k1}, s_{k1} s_{k2}$ , and  $s_{k2}p_i$ , where  $s_{k1}$  and  $s_{k2}$  are two pseudo-Steiner points as defined in Definition 2), we generate the coordinates information of the three sub-paths for all XRPs, and thus generate the second table, which is called multi-layer XRP-coordinates table (MLXCT). In Step 3, MLXR first inspects each edge of 3D-OFMST, and converts the edge into an XRP based on table lookup, thus generateing an ML-XST. Then, all those ML-XST edges that run through the obstacle are divided into tree types by MLXR, and some pseudo-Steiner points and legal via locations (if the via of an ML-XST edge is illegal) are found on the routing layers by employing three different strategies. Using these pseudo-Steiner points and legal vias as intermediate positions, MLXR can help all ML-XST edges successfully avoid all obstacles, thus generating an ML-OAXST. Finally, in Step 4, we use an operation called 'sliding' to attempt to divide a rectilinear path between two selected pseudo-Steiner points on the same layer into several sub-paths, such that the wire-length is reduced after division. In addition, given that for any one vertice of ML-OAXST, there always exists at least one optimal structure for its connection, we optimize the whole connection structure of ML-OAXST by first computing the optimal structure of each vertice, and then applying these structures to the original ML-OAXST until the XRP choice of all routing paths has been determined.

Experimental results. We implemented the proposed algorithm in the C/C++ language, and conducted all experiments on a PC with 2.9 GHz CPU and 2 GB memory. There are ten benchmark circuits in total. The first five groups are industrial test cases from Synopsys, the others were generated by Lin et al. [1] based on other five industrial test cases. We requested binaries from the authors of [1,2,6], and ran them on our PC for experiment comparison. Figure 1(d) shows the experimental results under  $C_v = 3$ .

The latest ML-OAXSMT algorithm was proposed by Liu et al. [6] based on the PSO algorithm, and the algorithm in [6] has achieved the best routing quality for the multi-layer obstacle-avoiding problem thus far. It can be seen that MLXR obtains 3.79% wire-length reduction on average, and runs 1383.29 times faster than [6]. Moreover, compared with the two latest ML-OARSMT algorithms [1,2], MLXR achieves 12.48% and 9.81% total cost reduction on average, respectively. With regard to runtime, MLXR achieves 102.21 and 2.48 times speedup on average compared with [1,2], respectively.

*Conclusion.* We studied the ML-OAXSMT construction problem for VLSI design, and proposed an efficient framework called MLXR. Several benchmark circuits groups were employed to validate the effectiveness of the proposed algorithm. The experiment results demonstrated the feasibility of our algorithm. Our future work will focus on the multi-layer timing-driven routing problem that considers the existence of obstacles.

Acknowledgements This work was supported in part by National Basic Research Program of China (Grant No. 2011CB808000), National Natural Science Foundation of China (Grants Nos. 11271002, 11501114), Fujian Natural Science Funds for Distinguished Young Scholar (Grant No. 2014J06017), and Program for New Century Excellent Talents in Fujian Province (Grant No. JA13021).

## References

- Lin C W, Chen S Y, Li C F, et al. Multilayer obstacleavoiding rectilinear Steiner tree construction based on spanning graphs. IEEE Trans Comput-Aided Des Integr Circuits Syst, 2008, 27: 2007–2016

- 2 Liu C H, Chen I C, Lee D T. An efficient algorithm for multi-layer obstacle-avoiding rectilinear Steiner tree construction. In: Proceedings of the 49th Annual Design Automation Conference. New York: ACM, 2012. 613–622

- 3 Shen W X, Cai Y C, Hong X L, et al. A single layer zero skew clock routing in X architecture. Sci China Ser F-Inf Sci, 2009, 52: 1466–1475

- 4 Huang X, Liu G, Guo W, et al. Obstacle-avoiding algorithm in X-architecture based on discrete particle swarm optimization for VLSI design. ACM Trans Des Autom Electron Syst, 2015, 20: 1–28

5 Ho T Y, Chang C F, Chang Y W, et al. Multilevel

- 5 Ho T Y, Chang C F, Chang Y W, et al. Multilevel full-chip routing for the X-based architecture. In: Proceedings of the 42nd Annual Design Automation Conference. New York: ACM, 2005. 597–602

- 6 Liu G, Huang X, Guo W, et al. Multilayer obstacleavoiding X-architecture Steiner minimal tree construction based on particle swarm optimization. IEEE Trans Syst Man Cybern B, 2015, 45: 989–1002

- 7 Lin Y C, Chien H A, Shih C C, et al. A multilayer obstacles-avoiding router using X-architecture. WSEAS Trans Circuits Syst, 2008, 7: 879–888

- 8 Bentley J L, Friedman J H. Fast algorithm for constructing minimal spanning trees in coordinate spaces. IEEE Trans Comput, 1978, 100: 97–105